# M30245 Group SINGLE-CHIP 16-BIT CMOS MICROCOMPUTER

REJ03B0005-0200 Rev.2.00 Oct 16, 2006

# **M30245 Group**

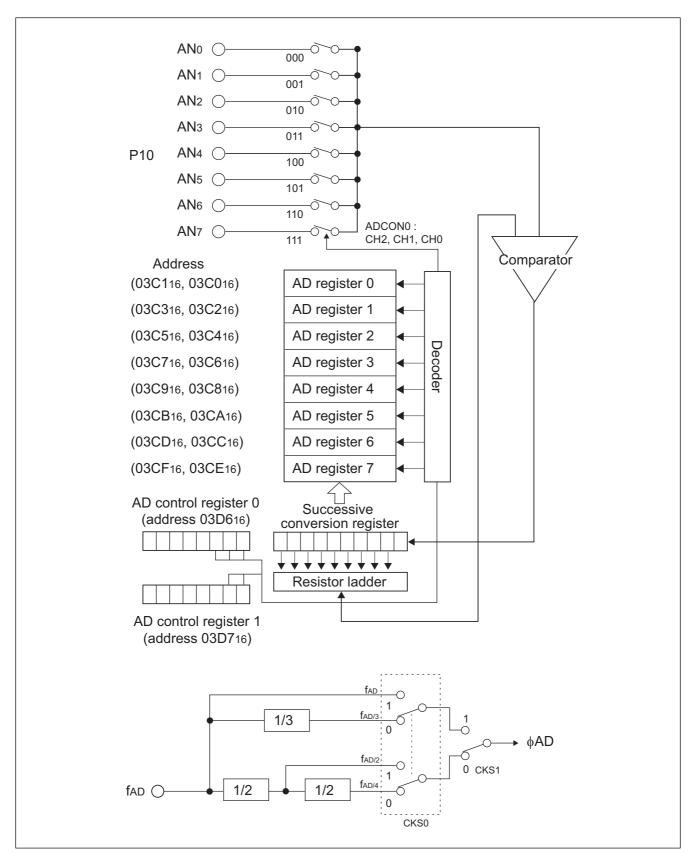

The M30245 group is a 16-bit microcomputer based on the M16C family core technology that uses a high performance silicon gate CMOS process with an M16C/62 Series CPU core. It comes packaged in a 100-pin molded plastic LQFP. They are single-chip USB peripheral microcontrollers that operate at Full Speed (12 Mbps) and are compliant with the Universal Serial Bus (USB) Version 2.0 specification. They also include many built-in peripherals including: A/D converter, Timers, UARTs, Serial Sound Interface, I<sup>2</sup>C, DMAC, CRC and more. These microcontrollers operate using sophisticated instructions featuring a high level of instruction efficiency, making them capable of executing instructions at high speed.

## **Features**

| i catares                           |                                                                         |

|-------------------------------------|-------------------------------------------------------------------------|

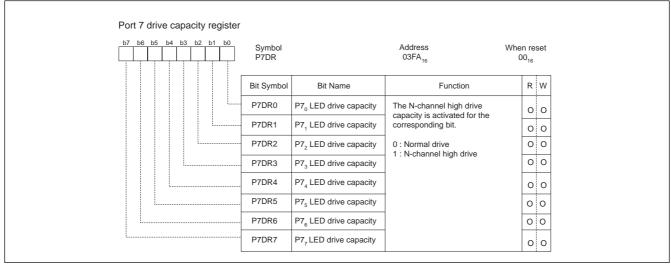

| Number of instructions              | 91                                                                      |

| Shortest instruction execution time | 62.5ns f(XIN)=16MHz, Vcc=3V with no wait                                |

| USB features:                       | Supports full-speed operation (12 Mbps)                                 |

|                                     | 3.25K programmable FIFO, 9 endpoints                                    |

|                                     | Integrated transceiver                                                  |

|                                     | Conforms to USB V 2.0 Specification                                     |

| Frequency synthesizer               | PLL for 48MHz clock                                                     |

| Memory capacity                     | 64K ROM / 5K RAM (M30245M8-XXXGP)                                       |

|                                     | 128K ROM / 10K RAM (M30245MC-XXXGP)                                     |

|                                     | 128K Flash /10K RAM (M30245FCGP)                                        |

| Supply voltage                      | 3.0 to 3.6V (f(XIN)=16MHz)                                              |

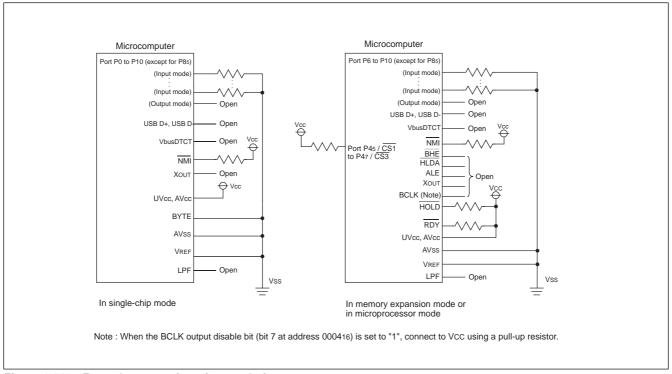

| Processor modes                     | Single chip, Memory expansion, Microprocessor                           |

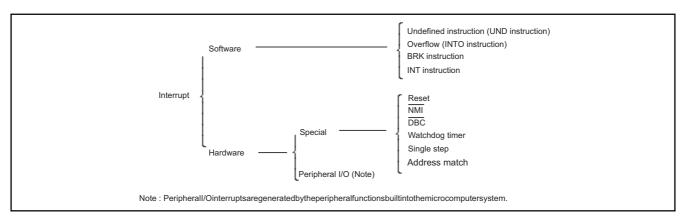

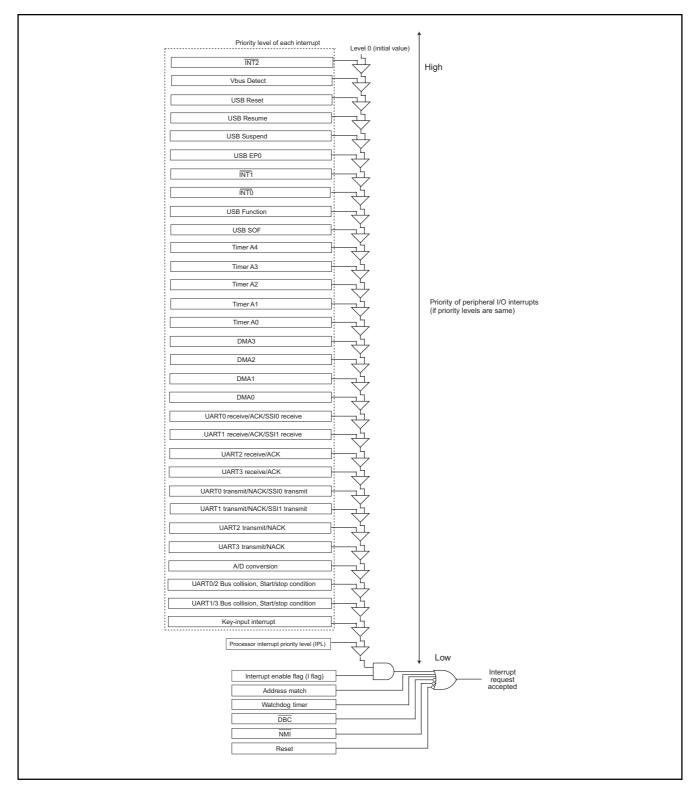

| Interrupts                          | 31 internal and 5 external interrupt sources                            |

|                                     | 4 software interrupt sources                                            |

|                                     | 7 levels (including key input interrupt X 8)                            |

| Multifunction 16-bit timer          | 5 16-bit timers                                                         |

| Serial Communication                | 2 X 7/8/9, 2 X 7/8/9/16/24/32 bits                                      |

|                                     | Configurable for synchronous or asynchronous mode,                      |

|                                     | Serial Sound Interface, I <sup>2</sup> C Bus                            |

| DMAC                                | 4 channels                                                              |

| A/D Converter                       | 10 bits X 8 channels                                                    |

| CRC calculation circuit             | 2 polynomials with MSB/LSB selectable                                   |

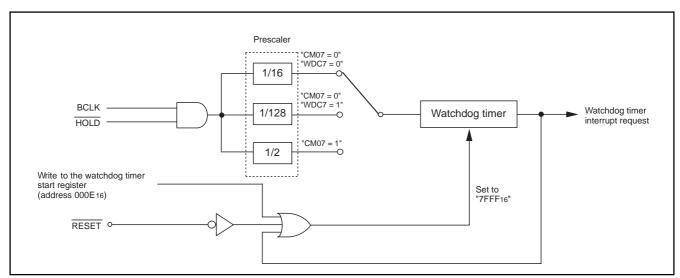

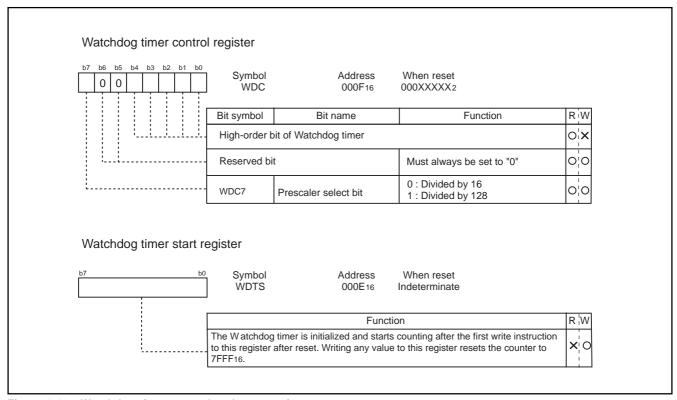

| Watchdog timer                      | 1 line                                                                  |

| Key-on wake up                      | 8 inputs                                                                |

| Programmable I/O                    | 82 lines                                                                |

| AND flash control circuit           | Built-in                                                                |

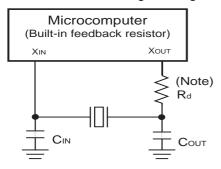

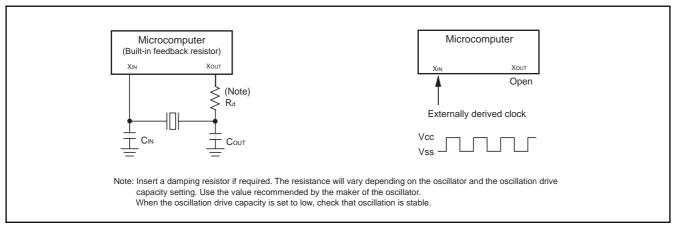

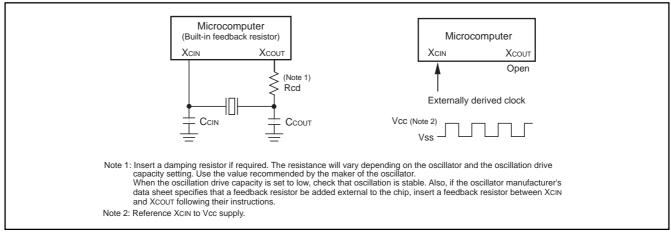

| Clock-generating circuit            | 2 built-in clock generation circuits                                    |

|                                     | (built-in feedback resistor, and external ceramic or quartz oscillator) |

|                                     |                                                                         |

# **Table of Contents**

| Features                                     |     |

|----------------------------------------------|-----|

| Description                                  | 3   |

| Memory                                       |     |

| Central Processing Unit                      |     |

| Reset                                        | 16  |

| Special Function Registers                   | 18  |

| Processor Modes                              | 26  |

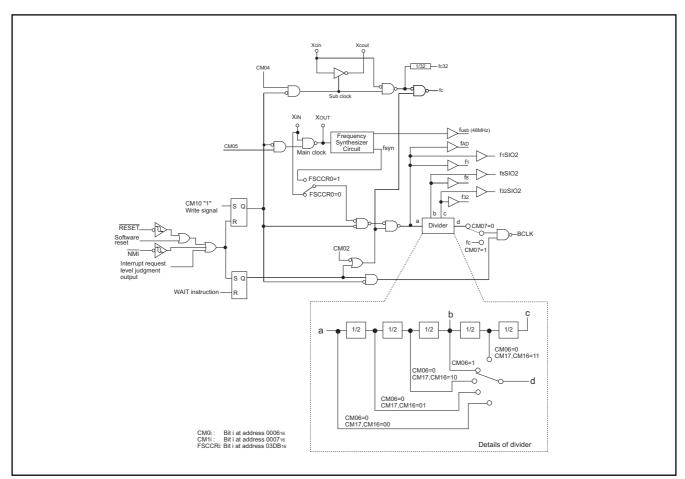

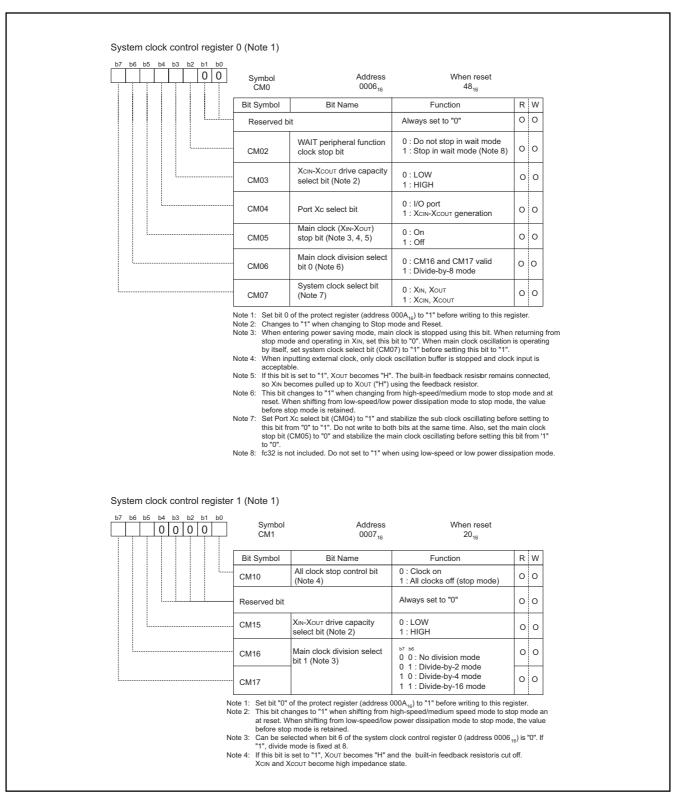

| System Clock                                 | 38  |

| Power Control                                |     |

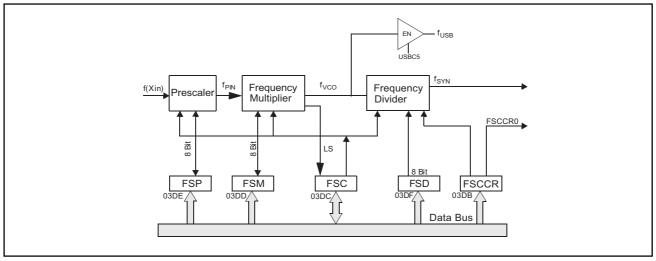

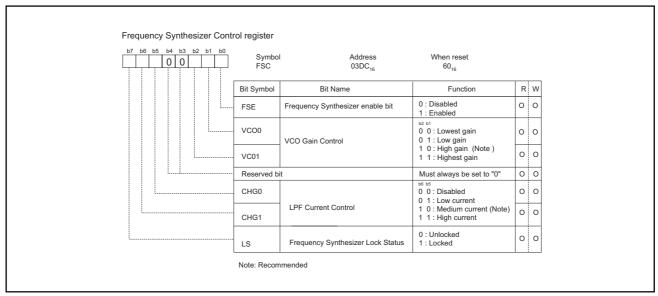

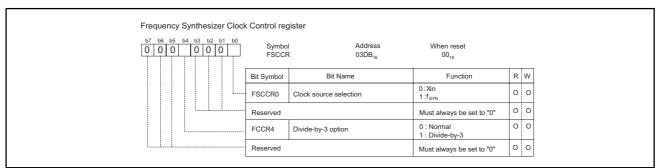

| Frequency synthesizer circuit                |     |

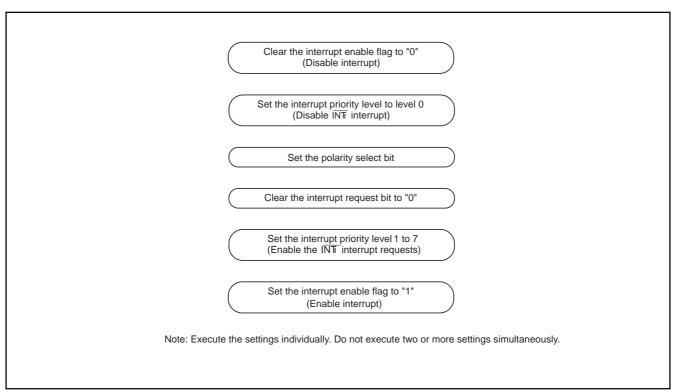

| Interrupts                                   | 50  |

| INT interrupt                                | 62  |

| NMI Interrupt                                | 62  |

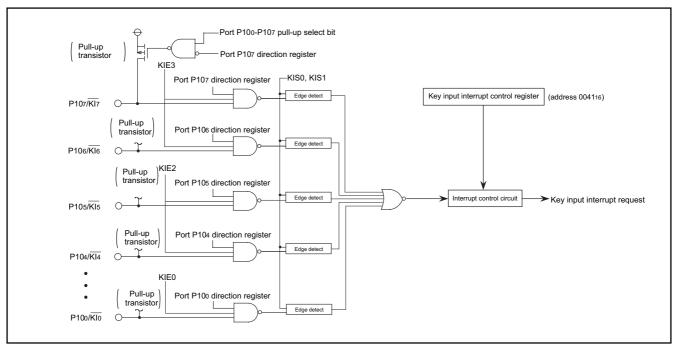

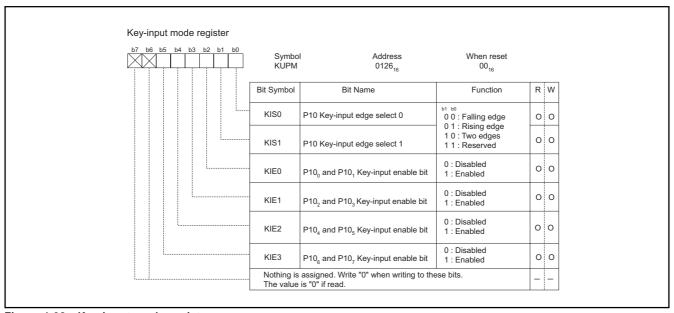

| Key-Input Interrupt                          | 62  |

| Address-Match Interrupt                      | 65  |

| Watchdog Timer                               | 68  |

| Universal Serial Bus                         | 70  |

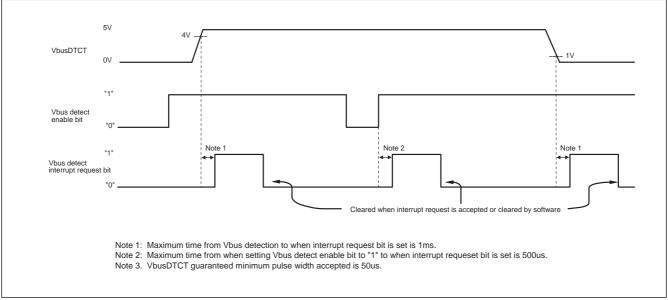

| Vbus Detect                                  |     |

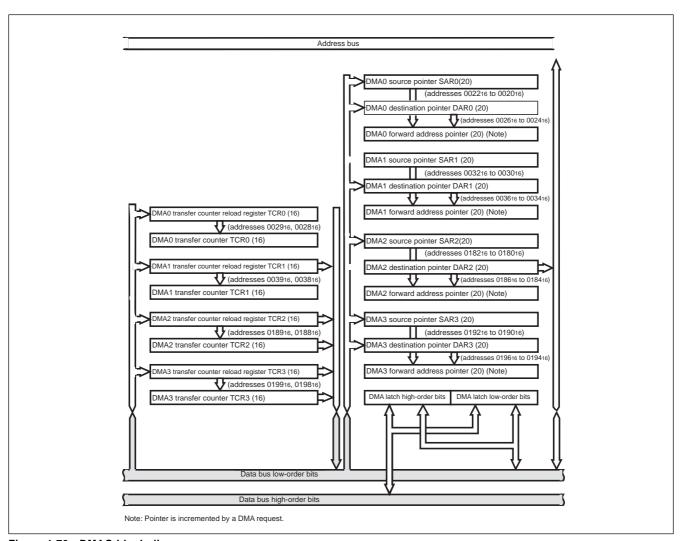

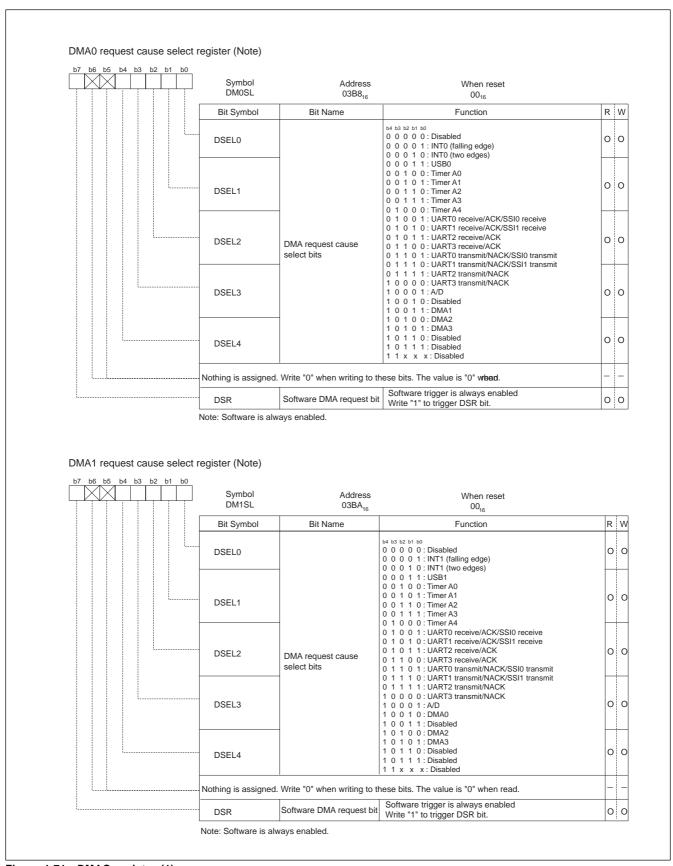

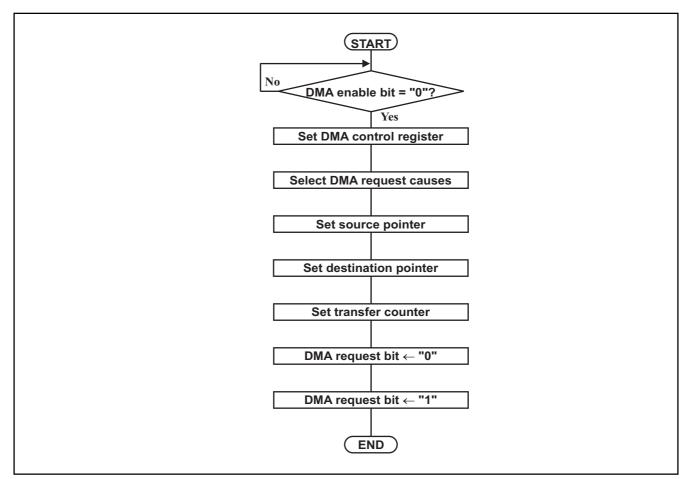

| Direct memory access controller              | 100 |

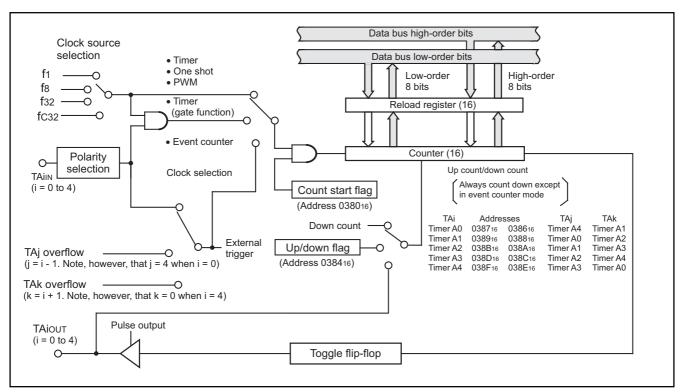

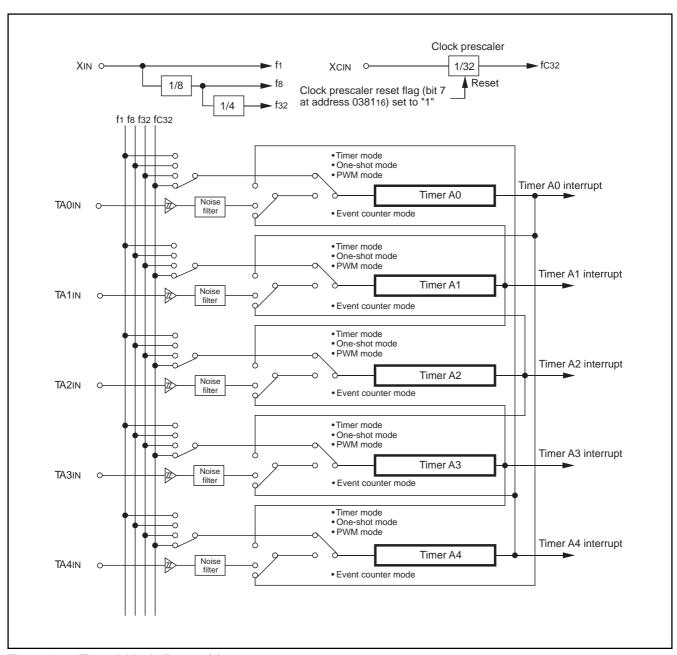

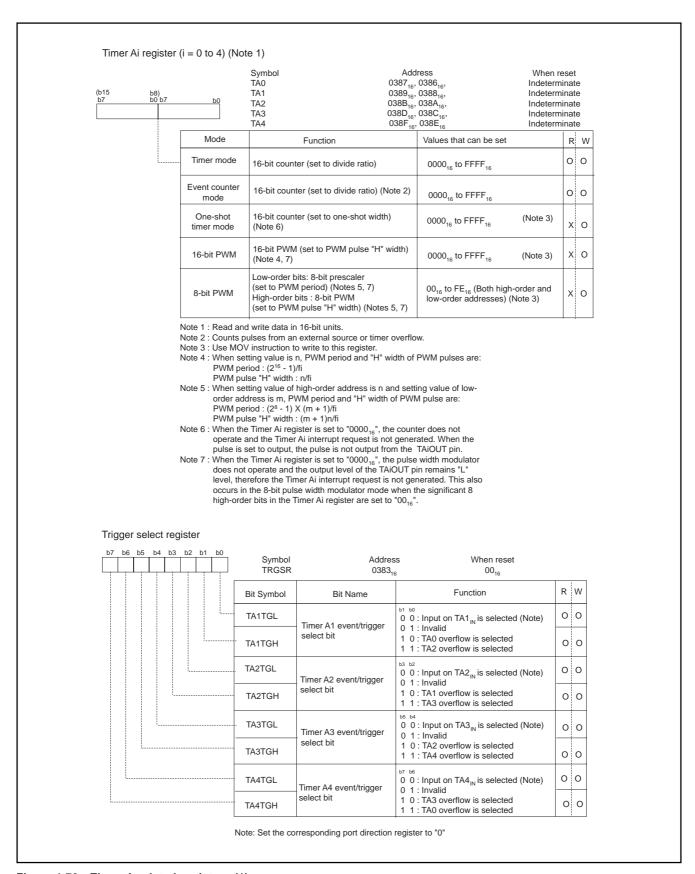

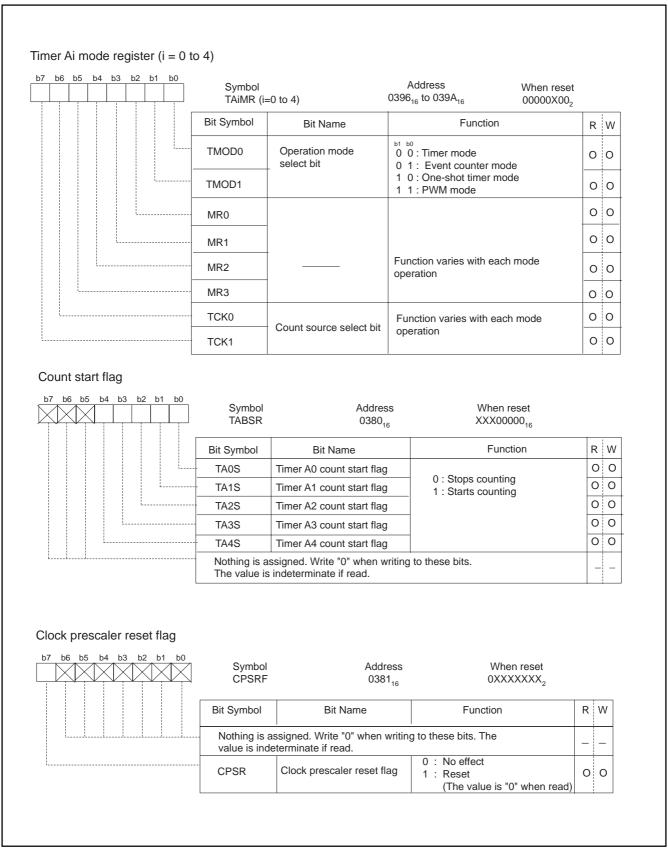

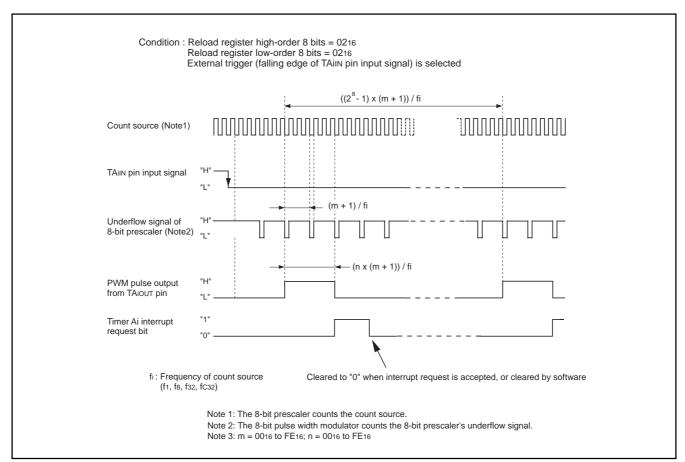

| Timer A                                      | 110 |

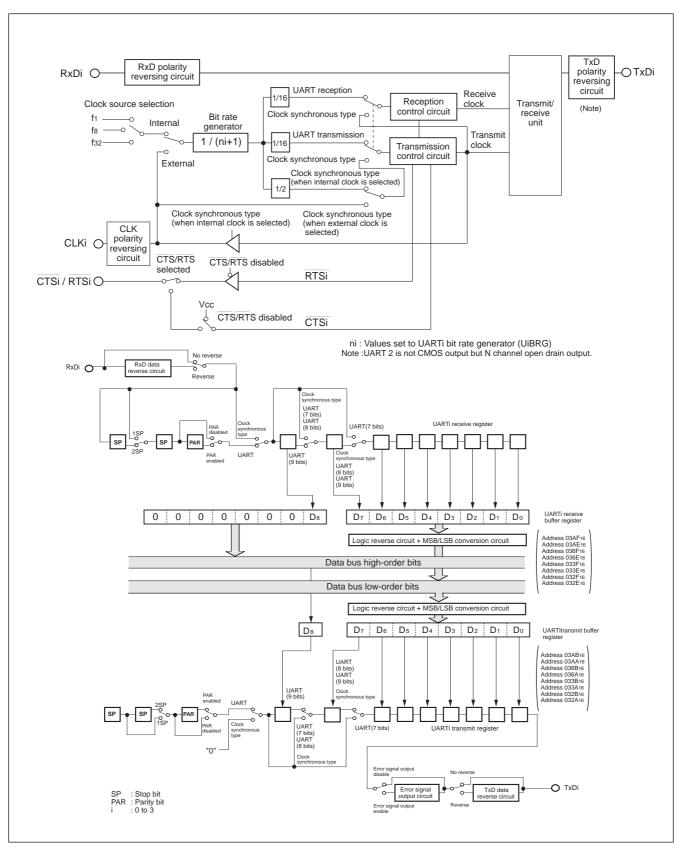

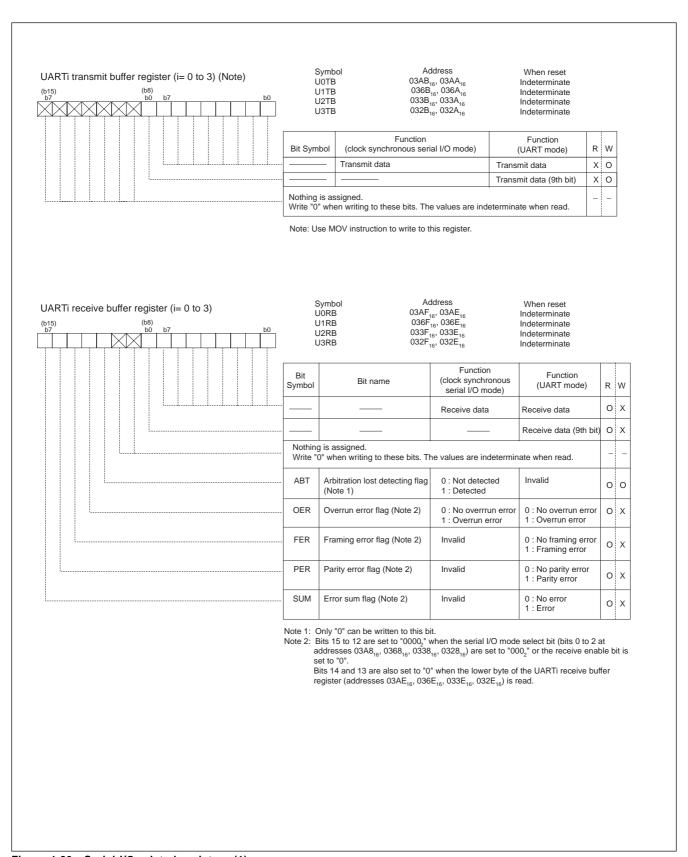

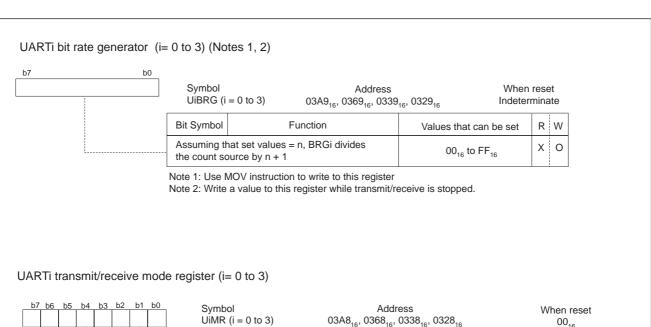

| Serial Communication                         | 125 |

| Clock synchronous serial I/O mode            |     |

| Clock asynchronous serial I/O (UART) mode    | 137 |

| UART mode (compliant with the SIM interface) | 142 |

| I <sup>2</sup> C Bus interface mode          | 145 |

| Serial Interface Special Function (SPI mode) | 151 |

| IE mode                                      |     |

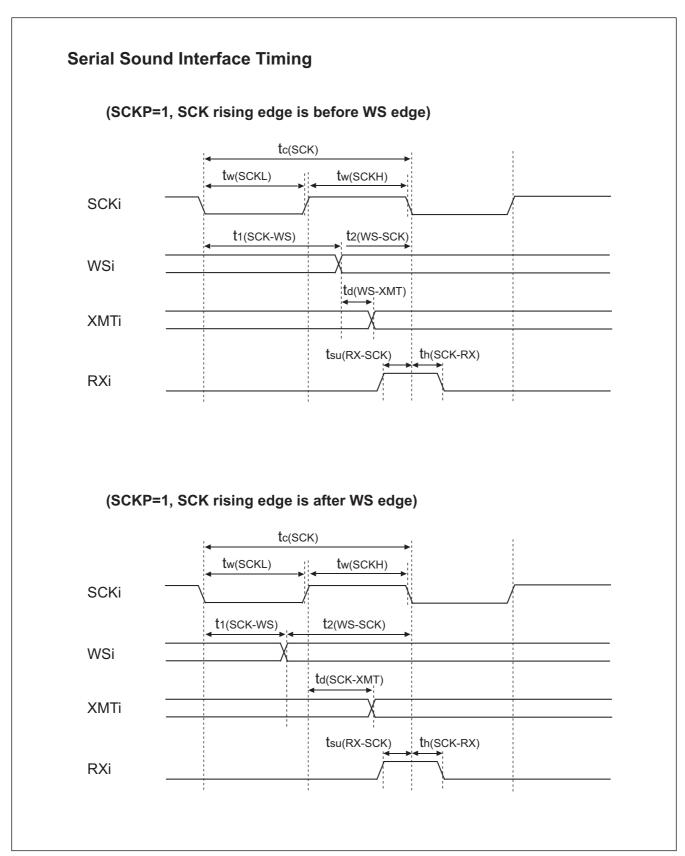

| Serial Sound Interface                       | 156 |

| A/D converter                                | 168 |

| CRC calculation circuit                      | 177 |

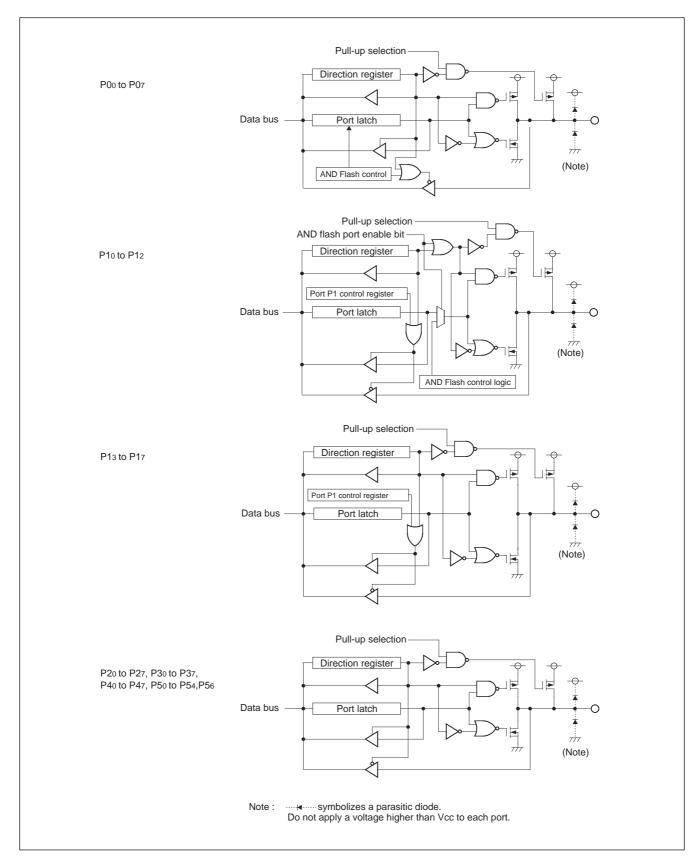

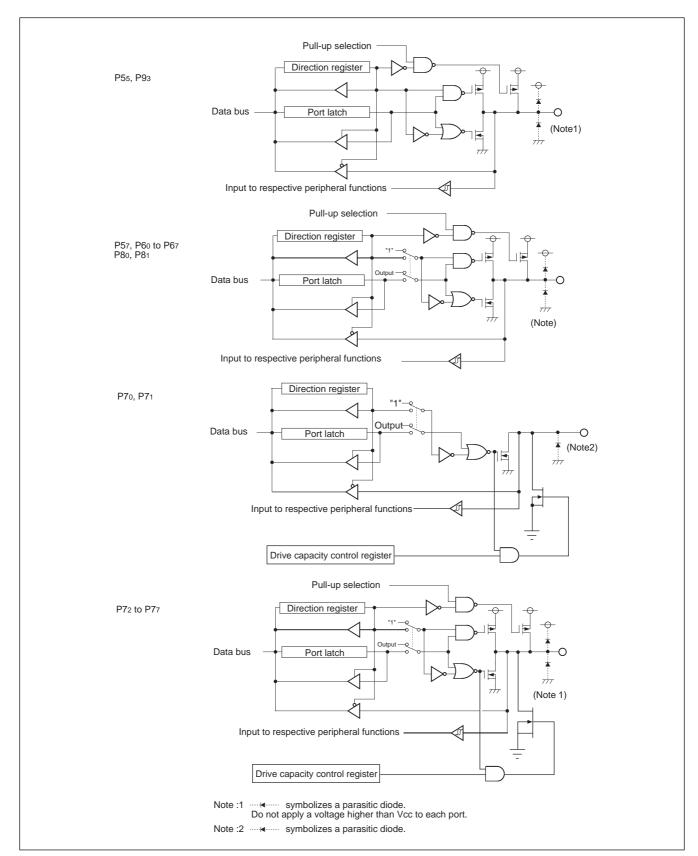

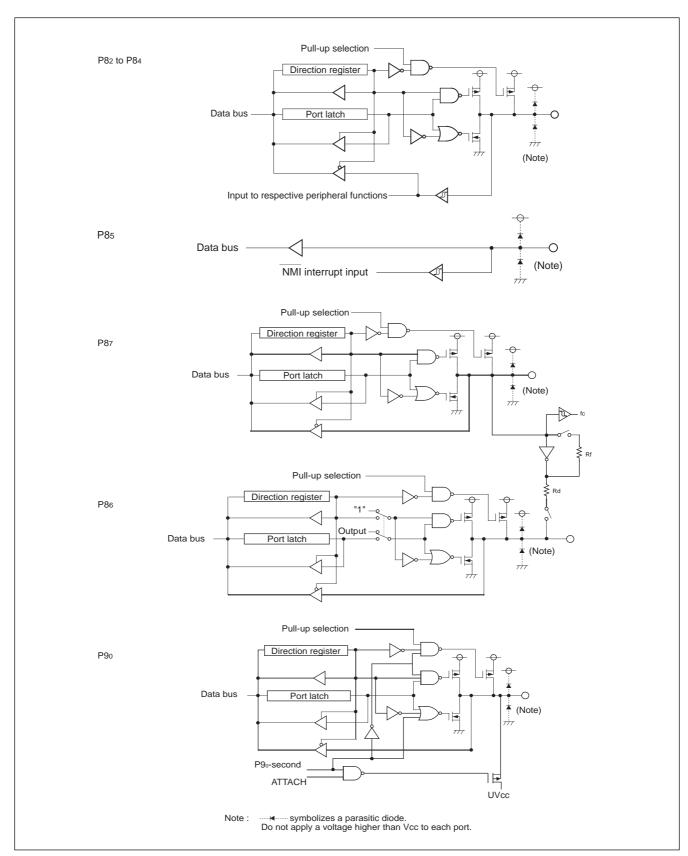

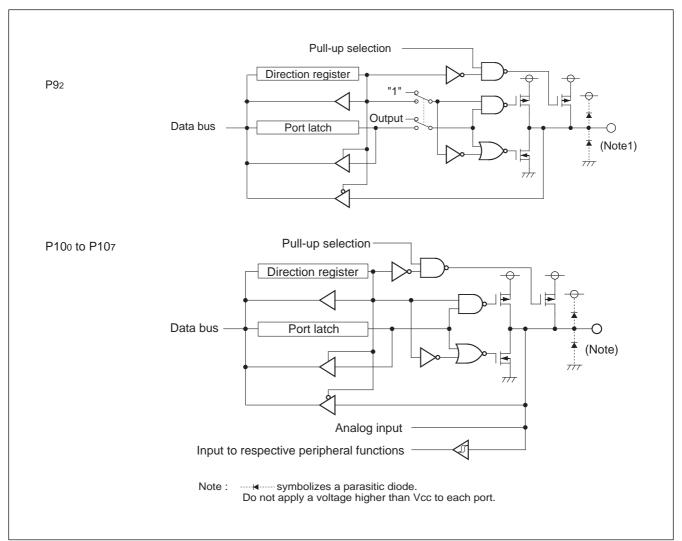

| Programmable I/O ports                       | 180 |

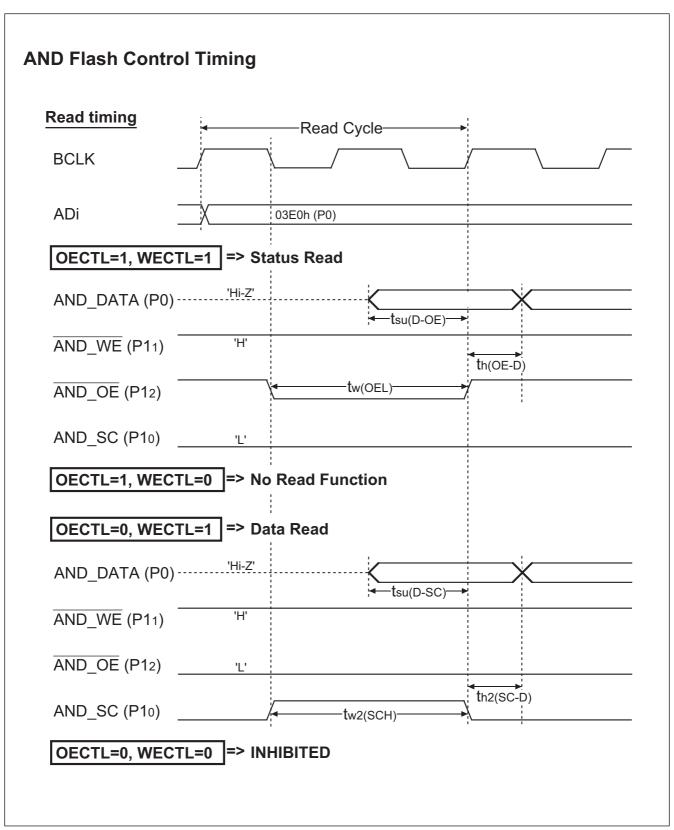

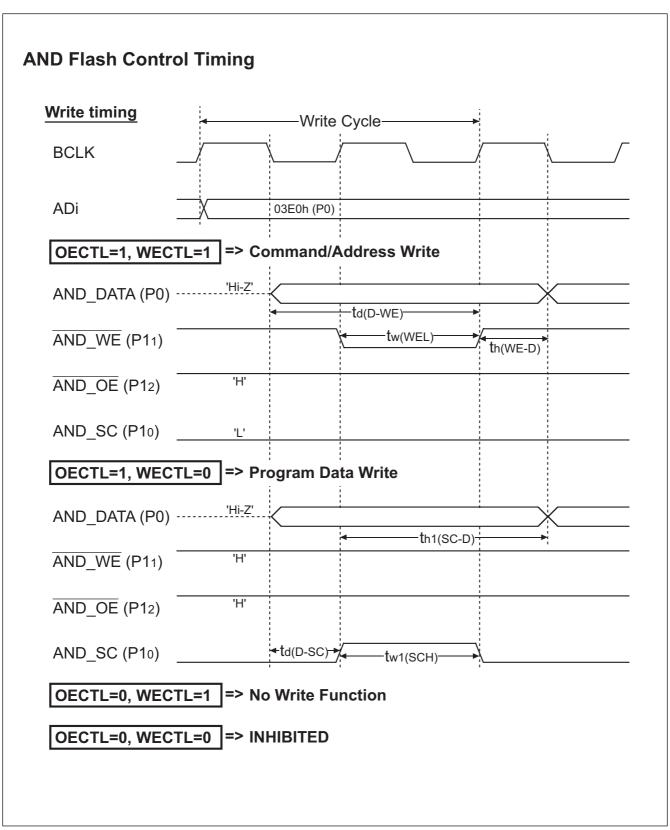

| AND Flash Control Circuit                    |     |

| Flash memory                                 | 195 |

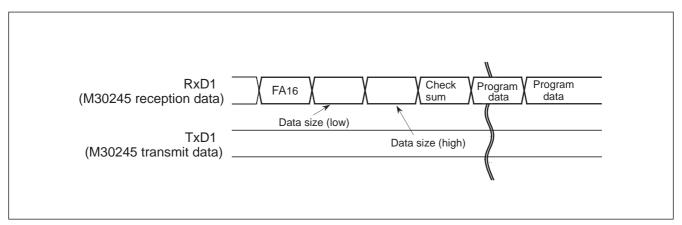

| CPU Rewrite Mode                             | 197 |

| Parallel I/O Mode                            | 206 |

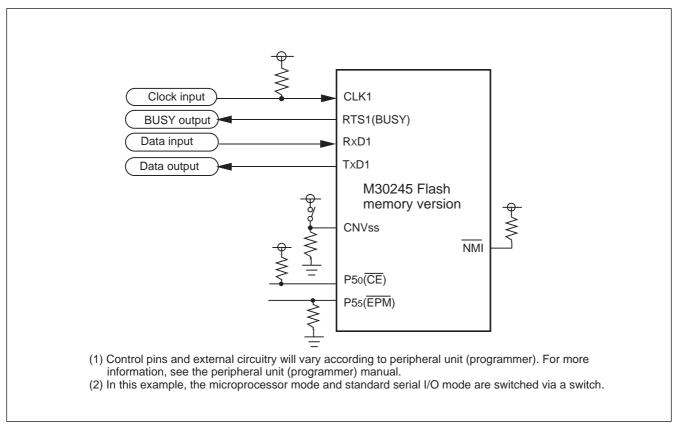

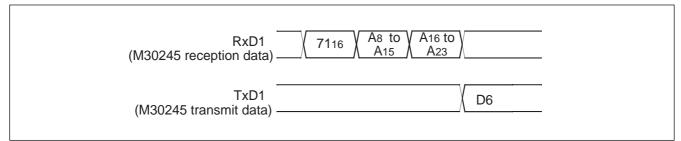

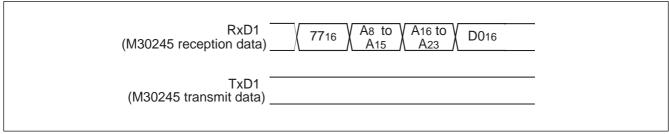

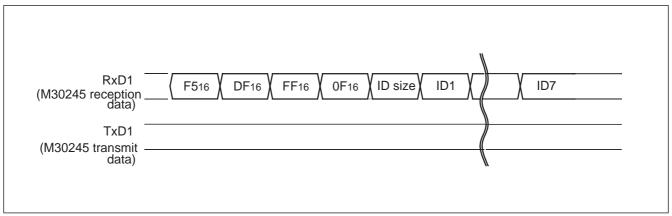

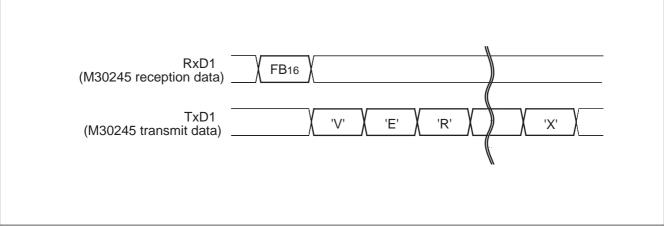

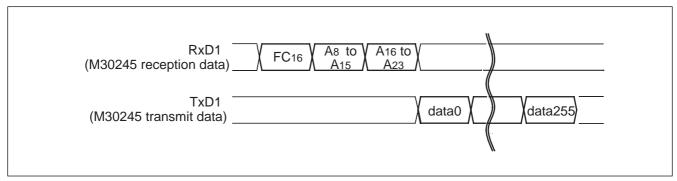

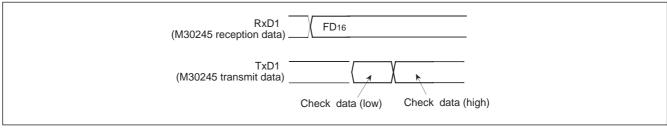

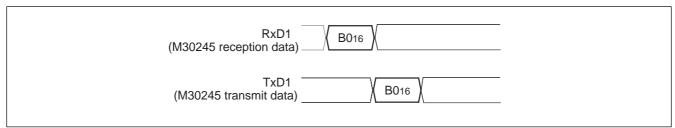

| Standard Serial I/O Mode                     | 208 |

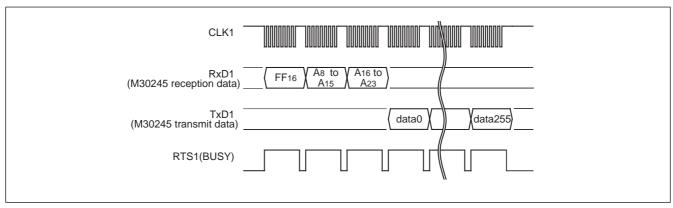

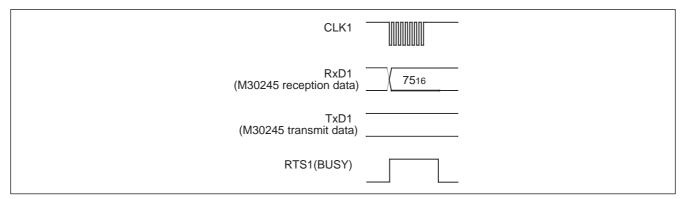

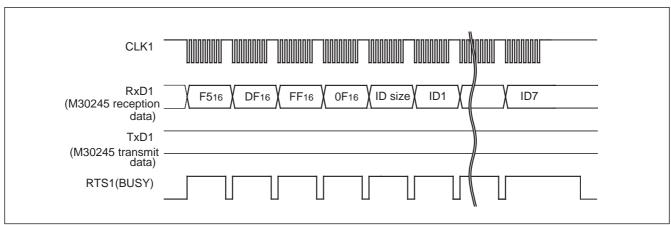

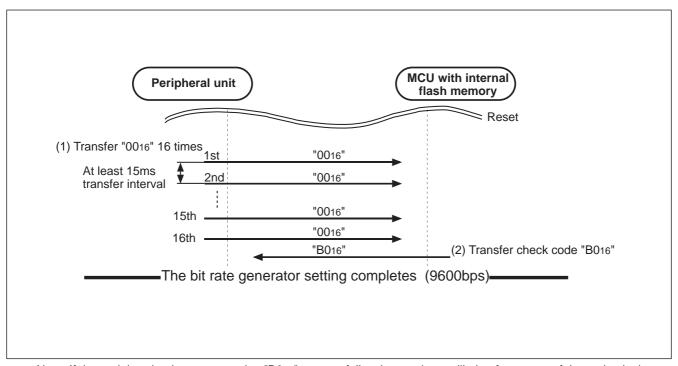

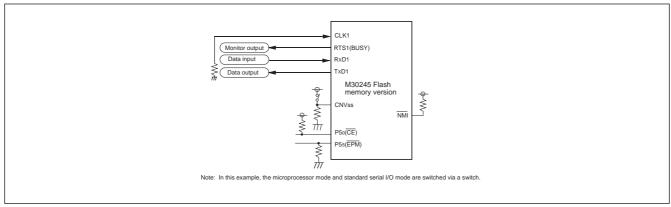

| Standard serial I/O mode 1                   | 211 |

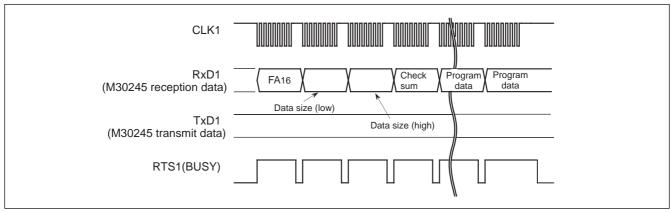

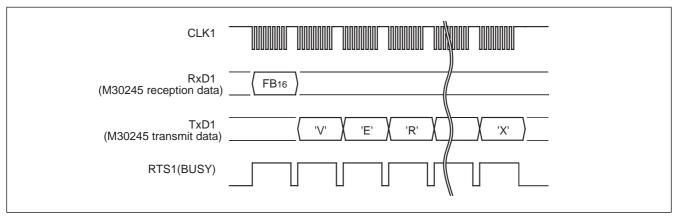

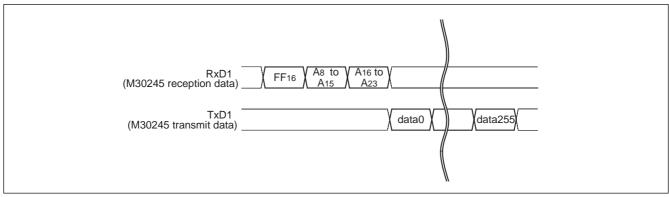

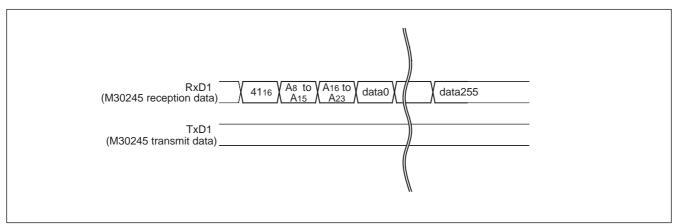

| Standard serial I/O mode 2                   |     |

| Electrical Specifications                    | 234 |

| Usage Notes                                  | 250 |

# **Applications**

USB peripherals, such as telephones, audio systems, office equipment, communications equipment, portable devices, scanners, digital cameras, and memory card readers.

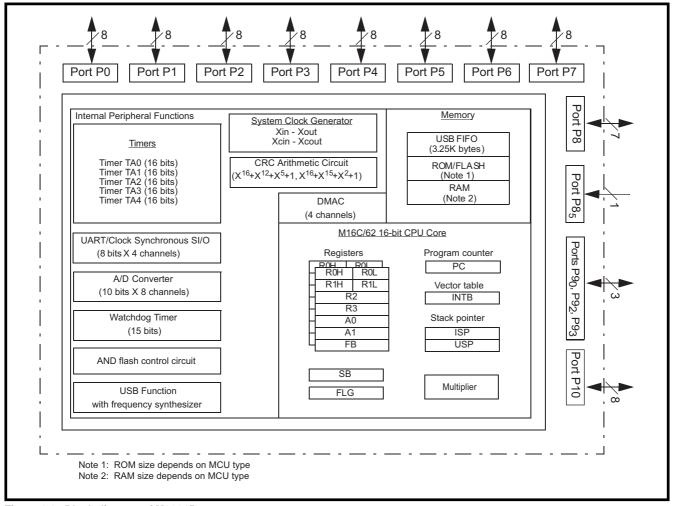

# **Block Diagram**

Figure 1.1 is a block diagram of the M30245 group.

Figure 1.1. Block diagram of M30245 group

# Performance outline

Table 1.1 is a performance outline of the M30245 group.

Table 1.1. M30245 Group performance outline

| Parameters                          |                          |                                                   | Function Description                                                                                         |  |  |  |

|-------------------------------------|--------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| Number of basic Instruction         | าร                       |                                                   | 91                                                                                                           |  |  |  |

| Shortest Instruction execution time |                          | 62.5 ns f(Xin)= 16 MHz, Vcc = 3V                  |                                                                                                              |  |  |  |

| Memory size                         | ROM                      |                                                   | 128/64 Kbytes                                                                                                |  |  |  |

|                                     | RAM                      |                                                   | 10/5 Kbytes                                                                                                  |  |  |  |

| Input/Output ports                  | P0 to P8, P10 (excl P85) | I/O                                               | 8 bits x 10                                                                                                  |  |  |  |

| input/Output ports                  | P85                      | I                                                 | 1 bit x 1                                                                                                    |  |  |  |

|                                     | P9                       | I/O                                               | 4 bits x 1                                                                                                   |  |  |  |

| Multifunction timer                 | TA0, TA1, TA2, TA3, TA4  |                                                   | 16 bits x 5                                                                                                  |  |  |  |

| Serial I/O                          | UART0 to 1               |                                                   | UART (or clock synchronous or Serial Sound Interface) x 2                                                    |  |  |  |

| Serial I/O                          | UART2 to 3               |                                                   | UART (or clock synchronous) x 2                                                                              |  |  |  |

| A/D converter                       |                          |                                                   | 10 bits x 8 channels                                                                                         |  |  |  |

| DMAC                                |                          |                                                   | 4 channels (31 trigger sources)                                                                              |  |  |  |

| CRC calculation circuits            |                          |                                                   | CRC-CCITT and CRC-16                                                                                         |  |  |  |

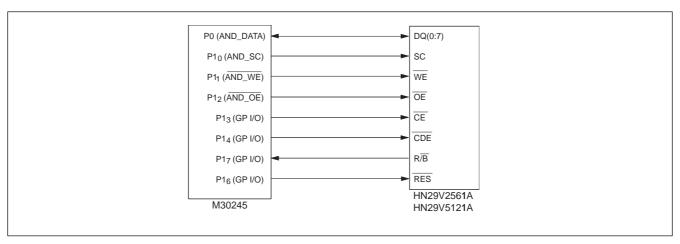

| AND flash control circuit           |                          |                                                   | Communicate with external AND type flash memory                                                              |  |  |  |

| Watchdog timer                      |                          |                                                   | 15 bits x 1 (with prescaler)                                                                                 |  |  |  |

| Interrupts                          |                          |                                                   | 31 internal, 4 external sources, 4 software, 7 levels                                                        |  |  |  |

| Clock-generating circuit            |                          |                                                   | 2 built-in clock generating circuits (built in feedback resistor, and external ceramic or quartz oscillator) |  |  |  |

| Supply voltage                      |                          | 3.0 ~ 3.6, f(XIN)=16MHz                           |                                                                                                              |  |  |  |

| Power consumption                   |                          | 25mA (Vcc=3.3V, f(XIN)=16MHz no division, USB ON) |                                                                                                              |  |  |  |

|                                     |                          |                                                   | 16mA (Vcc=3.3V, f(XIN)=16MHz no division, USB OFF)                                                           |  |  |  |

| Operating temperature               |                          |                                                   | -20 to 85°C                                                                                                  |  |  |  |

| Package                             |                          |                                                   | 100-pin plastic mold LQFP                                                                                    |  |  |  |

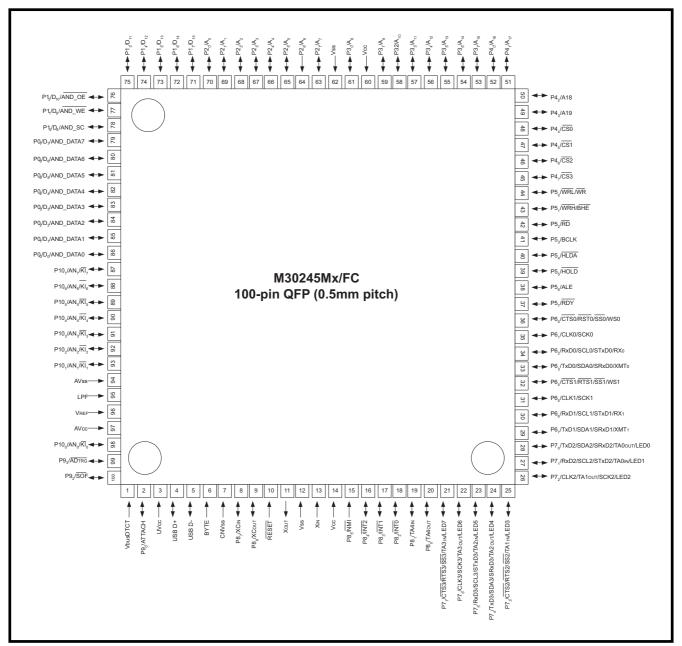

# **Pin Configuration**

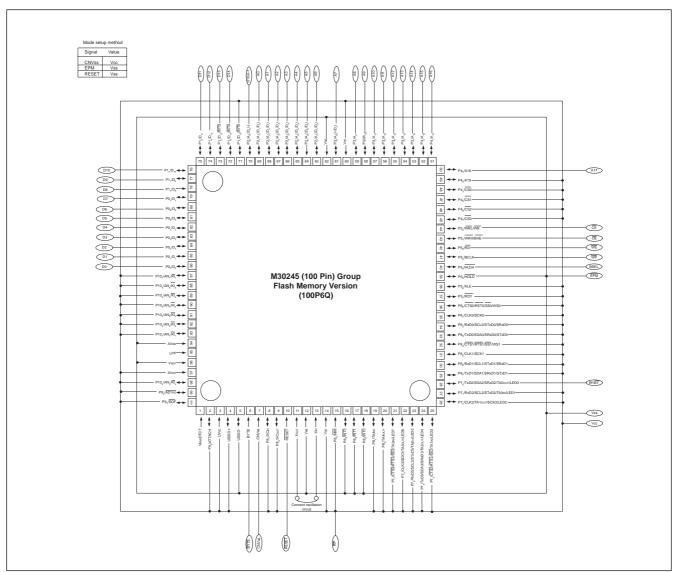

Figure 1.2 shows the pin configuration (top view). Table 1.2 lists the pin cross references and Table 1.3 describes the pin functions.

Figure 1.2. Pin Configuration (top view)

Table 1.2. Pin cross reference

| Pin<br>No. | Control    | Port            | Interrupt    | Timer                                            | UART/<br>USB | SPI   | I <sup>2</sup> C | Serial Sound<br>Interface | Analog/<br>Other | Bus Control |

|------------|------------|-----------------|--------------|--------------------------------------------------|--------------|-------|------------------|---------------------------|------------------|-------------|

| 1          |            |                 |              |                                                  | Vbus DTCT    |       |                  |                           |                  |             |

| 2          |            | P9 <sub>0</sub> |              |                                                  | ATTACH       |       |                  |                           |                  |             |

| 3          | UVcc       |                 |              |                                                  |              |       |                  |                           |                  |             |

| ļ.         |            |                 |              |                                                  | USB D+       |       |                  |                           |                  |             |

| 5          |            |                 |              |                                                  | USB D-       |       |                  |                           |                  |             |

| 3          | BYTE       |                 |              |                                                  |              |       |                  |                           |                  |             |

| 7          | CNVss      | D0              |              |                                                  |              |       |                  |                           |                  |             |

| 3          | XCIN       | P8 <sub>7</sub> | -            |                                                  |              |       |                  |                           |                  |             |

| )          | XCOUT      | P8 <sub>6</sub> |              |                                                  |              |       |                  |                           |                  |             |

| 10<br>I1   | RESET      |                 |              |                                                  |              |       |                  |                           |                  |             |

|            | Xout       |                 |              |                                                  |              |       |                  |                           |                  |             |

| 3          | Vss<br>XIN |                 | -            |                                                  |              |       |                  |                           |                  |             |

| 14         | Vcc        |                 |              |                                                  |              |       |                  |                           |                  |             |

| 15         | V 0.0      | P8 <sub>5</sub> | NMI          |                                                  |              |       | +                |                           |                  |             |

| 16         |            | P8 <sub>4</sub> | INT2         | <del> </del>                                     |              |       |                  |                           |                  |             |

| 7          |            | P8 <sub>3</sub> | INT1         |                                                  |              |       |                  |                           |                  |             |

| 18         |            | P8 <sub>2</sub> | INTO         | <del>                                     </del> | 1            |       |                  |                           |                  |             |

| 19         |            | P8 <sub>1</sub> | 11110        | TA4IN                                            |              | 1     |                  |                           |                  |             |

| 20         |            | -               |              | TA40UT                                           |              |       |                  |                           |                  |             |

| 21         |            | P8 <sub>0</sub> |              | TA3IN                                            | CTS3/RTS3    | SS3   |                  |                           | LED7             |             |

|            |            | P7 <sub>7</sub> |              |                                                  |              |       | CLICA            |                           |                  |             |

| 22         |            | P7 <sub>6</sub> | -            | TA3out                                           | CLK3         | SCK3  | CLK3             |                           | LED6             |             |

| 23         |            | P7 <sub>5</sub> |              | TA2IN                                            | RxD3         | STxD3 | SCL3             |                           | LED5             |             |

| 24         |            | P7 <sub>4</sub> | -            | TA2out                                           | TxD3         | SRxD3 | SDA3             |                           | LED4             |             |

| 25         |            | P7 <sub>3</sub> |              | TA1IN                                            | CTS2/RTS2    | SS2   | 21112            |                           | LED3             |             |

| 26         |            | P7 <sub>2</sub> |              | TA1out                                           | CLK2         | SCK2  | CLK2             |                           | LED2             |             |

| 27         |            | P7 <sub>1</sub> |              | TA0IN                                            | RxD2         | STxD2 | SCL2             |                           | LED1             |             |

| 28         |            | P7 <sub>0</sub> |              | TA0out                                           | TxD2         | SRxD2 | SDA2             |                           | LED0             |             |

| 29         |            | P6 <sub>7</sub> |              |                                                  | TxD1         | SRxD1 | SDA1             | XMT1                      |                  |             |

| 30         |            | P6 <sub>6</sub> |              |                                                  | RxD1         | STxD1 | SCL1             | RX1                       |                  |             |

| 31         |            | P6 <sub>5</sub> |              |                                                  | CLK1         | SCK1  | CLK1             | SCK1                      |                  |             |

| 32         |            | P6 <sub>4</sub> |              |                                                  | CTS1/RTS1    | SS1   |                  | WS1                       |                  |             |

| 33         |            | P6 <sub>3</sub> |              |                                                  | TxD0         | SRxD0 | SDA0             | XMT <sub>0</sub>          |                  |             |

| 34         |            | P6 <sub>2</sub> |              |                                                  | RxD0         | STxD0 | SCL0             | RX0                       |                  |             |

| 35         |            | P6 <sub>1</sub> |              |                                                  | CLK0         | SCK0  | CLK0             | SCK0                      |                  |             |

| 36         |            | P6 <sub>0</sub> |              |                                                  | CTS0/RTS0    | SS0   |                  | WS0                       |                  |             |

| 37         |            | P5 <sub>7</sub> |              |                                                  |              |       |                  |                           |                  | RDY         |

| 38         |            | P5 <sub>6</sub> |              |                                                  |              |       |                  |                           |                  | ALE         |

| 39         |            | P5 <sub>5</sub> |              |                                                  |              |       |                  |                           |                  | HOLD        |

| 10         |            | P5 <sub>4</sub> |              |                                                  |              |       |                  |                           |                  | HLDA        |

| <b>‡</b> 1 |            | P5 <sub>3</sub> |              |                                                  |              |       |                  |                           |                  | BCLK        |

| 12         |            | P5 <sub>2</sub> |              |                                                  |              |       |                  |                           |                  | RD          |

| 13         |            | P5 <sub>1</sub> |              |                                                  |              |       |                  |                           |                  | WRH/BHE     |

| 14         |            | P5 <sub>0</sub> |              |                                                  |              |       |                  |                           |                  | WRL/WR      |

| 15         |            | P4 <sub>7</sub> |              |                                                  |              |       |                  |                           |                  | CS3         |

| 16         |            | P4 <sub>6</sub> |              | 1                                                |              |       |                  |                           |                  | CS2         |

| 17         |            | P4 <sub>5</sub> |              |                                                  | 1            | 1     | 1                |                           |                  | CS1         |

| 18         |            | P4 <sub>4</sub> |              |                                                  | 1            |       |                  |                           |                  | CS0         |

| 19         |            | P4 <sub>3</sub> |              |                                                  | 1            |       |                  |                           |                  | A19         |

| 50         |            | P4 <sub>2</sub> |              |                                                  | 1            |       |                  |                           |                  | A18         |

| 51         |            | P4 <sub>1</sub> | <del> </del> |                                                  |              | 1     | +                | +                         |                  | A17         |

Table 1.2 Pin cross reference

| Pin<br>No. | Control | Port             | Interrupt       | Timer | UART/<br>USB | SPI | I <sup>2</sup> C | Serial Sound<br>Interface | Analog/<br>Other  | Bus Control     |

|------------|---------|------------------|-----------------|-------|--------------|-----|------------------|---------------------------|-------------------|-----------------|

| 52         |         | P4 <sub>0</sub>  |                 |       |              |     |                  |                           |                   | A <sub>16</sub> |

| 53         |         | P3 <sub>7</sub>  |                 |       |              |     |                  |                           |                   | A <sub>15</sub> |

| 54         |         | P3 <sub>6</sub>  |                 |       |              |     |                  |                           |                   | A <sub>14</sub> |

| 55         |         | P3 <sub>5</sub>  |                 |       |              |     |                  |                           |                   | A <sub>13</sub> |

| 56         |         | P3 <sub>4</sub>  |                 |       |              |     |                  |                           |                   | A <sub>12</sub> |

| 57         |         | P3 <sub>3</sub>  |                 |       |              |     |                  |                           |                   | A <sub>11</sub> |

| 58         |         | P3 <sub>2</sub>  |                 |       |              |     |                  |                           |                   | A <sub>10</sub> |

| 59         |         | P3 <sub>1</sub>  |                 |       |              |     |                  |                           |                   | A <sub>9</sub>  |

| 60         | Vcc     |                  |                 |       |              |     |                  |                           |                   |                 |

| 61         |         | P3 <sub>0</sub>  |                 |       |              |     |                  |                           |                   | A <sub>8</sub>  |

| 62         | Vss     |                  |                 |       |              |     |                  |                           |                   |                 |

| 63         |         | P2 <sub>7</sub>  |                 |       |              |     |                  |                           |                   | A <sub>7</sub>  |

| 64         |         | P2 <sub>6</sub>  |                 |       |              |     |                  |                           |                   | A <sub>6</sub>  |

| 65         |         | P2 <sub>5</sub>  |                 |       |              |     |                  |                           |                   | A <sub>5</sub>  |

| 66         |         | P2 <sub>4</sub>  |                 |       |              |     |                  |                           |                   | A <sub>4</sub>  |

| 67         |         | P2 <sub>3</sub>  |                 |       |              |     |                  |                           |                   | $A_3$           |

| 68         |         | P2 <sub>2</sub>  |                 |       |              |     |                  |                           |                   | A <sub>2</sub>  |

| 69         |         | P2 <sub>1</sub>  |                 |       |              |     |                  |                           |                   | A <sub>1</sub>  |

| 70         |         | P2 <sub>0</sub>  |                 |       |              |     |                  |                           |                   | A <sub>0</sub>  |

| 71         |         | P1 <sub>7</sub>  |                 |       |              |     |                  |                           |                   | D <sub>15</sub> |

| 72         |         | P1 <sub>6</sub>  |                 |       |              |     |                  |                           |                   | D <sub>14</sub> |

| 73         |         | P1 <sub>5</sub>  |                 |       |              |     |                  |                           |                   | D <sub>13</sub> |

| 74         |         | P1 <sub>4</sub>  |                 |       |              |     |                  |                           |                   | D <sub>12</sub> |

| 75         |         | P1 <sub>3</sub>  |                 |       |              |     |                  |                           |                   | D <sub>11</sub> |

| 76         |         | P1 <sub>2</sub>  |                 |       |              |     |                  |                           | AND_OE            | D <sub>10</sub> |

| 77         |         | P1 <sub>1</sub>  |                 |       |              |     |                  |                           | AND_WE            | D <sub>9</sub>  |

| 78         |         | P1 <sub>0</sub>  |                 |       |              |     |                  |                           | AND_SC            | D <sub>8</sub>  |

| 79         |         | P0 <sub>7</sub>  |                 |       |              |     |                  |                           | AND_DATA7         |                 |

| 80         |         | P0 <sub>6</sub>  |                 |       |              |     |                  |                           | AND_DATA6         |                 |

| 81         |         | P0 <sub>5</sub>  |                 |       |              |     |                  |                           | AND_DATA5         | ļ <u>"</u>      |

| 82         |         | P0 <sub>4</sub>  |                 |       |              |     |                  |                           | AND_DATA4         | ļ               |

| 83         |         | P0 <sub>3</sub>  |                 |       |              |     |                  |                           | AND_DATA3         |                 |

| 84         |         | P0 <sub>2</sub>  |                 |       |              |     |                  |                           | AND_DATA2         | -               |

| 85         |         | P0 <sub>1</sub>  |                 |       |              |     |                  |                           | AND_DATA1         |                 |

| 86         |         | P0 <sub>0</sub>  |                 |       |              |     |                  |                           | AND_DATA0         |                 |

| 87         |         | P10 <sub>7</sub> | KI <sub>7</sub> |       |              |     |                  |                           | AN <sub>7</sub>   | 0               |

| 88         |         | P10 <sub>6</sub> | KI <sub>6</sub> |       |              |     |                  |                           | AN <sub>6</sub>   |                 |

| 89         |         | P10 <sub>5</sub> | KI <sub>5</sub> |       |              |     |                  | †                         | AN <sub>5</sub>   |                 |

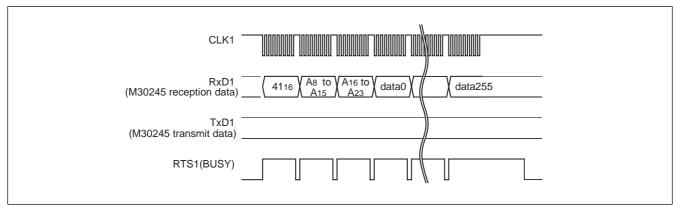

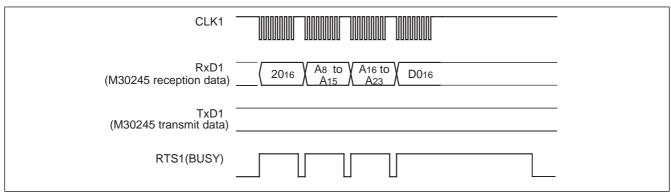

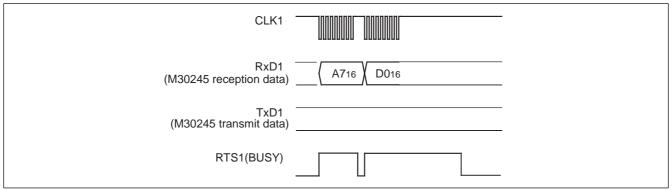

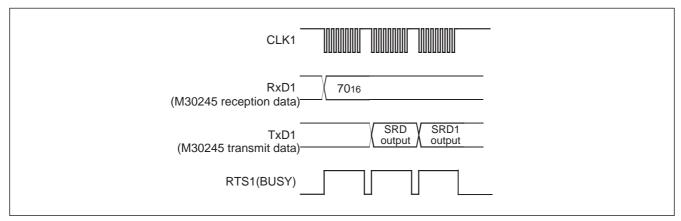

| 90         |         | P10 <sub>4</sub> | KI <sub>4</sub> |       |              |     |                  | 1                         | AN <sub>4</sub>   |                 |

| 91         |         | P10 <sub>3</sub> | KI <sub>3</sub> |       |              |     |                  | +                         | AN <sub>3</sub>   |                 |

| 92         |         | P10 <sub>2</sub> | KI <sub>2</sub> |       |              |     |                  | +                         | AN <sub>2</sub>   |                 |

| 93         |         | P10 <sub>2</sub> | KI <sub>2</sub> |       |              |     |                  |                           | AN <sub>1</sub>   |                 |

| 94         | AVss    | 1 101            | 137             |       |              |     |                  |                           | 7 11 17           |                 |

| 95         | LPF     |                  |                 |       |              |     |                  | +                         |                   |                 |

| 96         |         |                  |                 |       |              |     |                  | 1                         | V <sub>REF</sub>  |                 |

| 97         | AVcc    |                  |                 |       |              |     |                  |                           | IXLI*             |                 |

| 98         |         | P10 <sub>0</sub> | ΚΙ <sub>0</sub> |       |              |     |                  |                           | AN <sub>0</sub>   |                 |

| 99         |         | P9 <sub>3</sub>  |                 |       |              |     |                  |                           | AD <sub>TRG</sub> |                 |

| 100        |         | P9 <sub>2</sub>  |                 |       | SOF          |     |                  | †                         | 1110              |                 |

Table 1.3 Pin description

| Port | Function                             | Pin Name                           | I/O | Description                                                                                                                                                                                                                                                                                                                                                                               |

|------|--------------------------------------|------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Power supply input                   | Vcc                                |     | 3.0 to 3.6V                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                      | Vss                                |     | 0V                                                                                                                                                                                                                                                                                                                                                                                        |

|      | CPU mode switch                      | CNVss                              | I   | Connect to Vss: single-chip or memory expansion mode Connect to Vcc: Microprocessor mode only                                                                                                                                                                                                                                                                                             |

|      | External data bus width select input | BYTE                               | I   | Selects external memory data bus width. Connect to Vss: 16-bit. Connect to Vcc: 8-bit.                                                                                                                                                                                                                                                                                                    |

|      | Reset input                          | RESET                              | - 1 | "L" resets the microcomputer.                                                                                                                                                                                                                                                                                                                                                             |

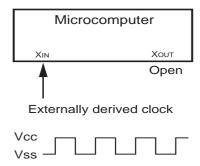

|      | Clock input                          | XIN                                | I   | These pins support the main clock generating circuit. Connect a crystal betwee                                                                                                                                                                                                                                                                                                            |

|      | Clock output                         | Хоит                               | 0   | the XIN and XOUT pins. To use an external clock, input it to the XIN pin and leav the XOUT pin open.                                                                                                                                                                                                                                                                                      |

|      | Analog power supply input            | AVcc                               |     | Connect to Vcc.                                                                                                                                                                                                                                                                                                                                                                           |

|      |                                      | AVss                               |     | Connect to Vss.                                                                                                                                                                                                                                                                                                                                                                           |

|      | Reference voltage input              | VREF                               | - 1 | This is a reference voltage for A/D converter.                                                                                                                                                                                                                                                                                                                                            |

|      | Low pass filter                      | LPF                                | 0   | Loop filter for the frequency synthesizer circuit.                                                                                                                                                                                                                                                                                                                                        |

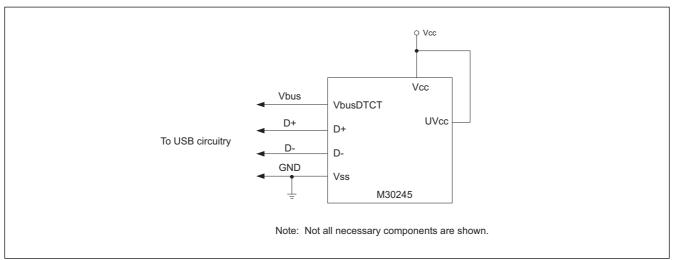

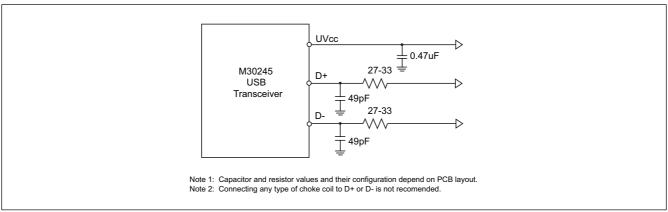

|      | USB power supply input               | UVcc                               |     | Power pin for USB                                                                                                                                                                                                                                                                                                                                                                         |

|      | Vbus detect                          | VbusDTCT                           | - 1 | Detects USB host power                                                                                                                                                                                                                                                                                                                                                                    |

|      | USB D+                               | USB D+                             | I/O | USB D+ voltage line interface                                                                                                                                                                                                                                                                                                                                                             |

|      | USB D-                               | USB D-                             | I/O | USB D- voltage line interface                                                                                                                                                                                                                                                                                                                                                             |

| P0   | I/O port                             | P0 <sub>0</sub> to P0 <sub>7</sub> | I/O | This is an 8-bit CMOS I/O port. The input/output port direction register allows each pin to be set individually. When used for input, the port can be set to include internal pull-up resistors in 4-pin blocks.                                                                                                                                                                          |

|      | Data bus                             | D <sub>0</sub> to D <sub>7</sub>   | I/O | These pins input and output 8 low-order data bits when set as a separate bus.                                                                                                                                                                                                                                                                                                             |

|      | AND Flash control                    | AND_DATA0 to 7                     | I/O | Data pins for communicating with AND type flash memory devices                                                                                                                                                                                                                                                                                                                            |

| P1   | I/O port                             | P1 <sub>0</sub> to P1 <sub>7</sub> | I/O | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                               |

|      | Data bus                             | D <sub>8</sub> to D <sub>15</sub>  | I/O | These pins input and output 8 high-order data bits when set as a separate bus.                                                                                                                                                                                                                                                                                                            |

|      | AND Flash control                    | AND_SC<br>AND_WE<br>AND_OE         | 0   | Control signal pins for communicating with AND type flash memory devices                                                                                                                                                                                                                                                                                                                  |

| P2   | I/O port                             | P2 <sub>0</sub> to P2 <sub>7</sub> | I/O | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                               |

|      | Address bus                          | A <sub>0</sub> to A <sub>7</sub>   | 0   | These pins output 8 low-order address bits.                                                                                                                                                                                                                                                                                                                                               |

| P3   | I/O port                             | P3 <sub>0</sub> to P3 <sub>7</sub> | I/O | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                               |

|      | Address bus                          | A <sub>8</sub> to A <sub>15</sub>  | 0   | These pins output 8 middle-order address bits.                                                                                                                                                                                                                                                                                                                                            |

| P4   | I/O port                             | P4 <sub>0</sub> to P4 <sub>7</sub> | I/O | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                               |

|      | Address bus                          | A <sub>16</sub> to A <sub>19</sub> | 0   | These pins output 4 high-order address bits.                                                                                                                                                                                                                                                                                                                                              |

|      | Chip select                          | CS0 to CS3                         | 0   | P4 <sub>4</sub> to P4 <sub>7</sub> are chip select output pins that specify access areas.                                                                                                                                                                                                                                                                                                 |

| P5   | I/O port                             | P5 <sub>0</sub> to P5 <sub>7</sub> | I/O | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                                                                                                                                                                                                               |

| гэ   | Bus control                          | WRL/WR                             |     | Ouput WRL, WRH (WR, BHE), and RD bus control signals. Using WRL and                                                                                                                                                                                                                                                                                                                       |

|      | DUS CONTROL                          | WRH/BHE<br>RD                      | 0 0 | WRH or WR and BHE can be switched using software control.  ■ WRL, WRH, and RD selected.  With a 16-bit external data bus, data is written to even addresses when the WRL signal is "L", and to the odd addresses when the WRH signal is "L". Data is read when RD is "L".  WR, BHE, and RD selected.  Data is written when WR is "L". Use this mode when using an 8-bit external data bus |

|      |                                      | BCLK                               | 0   | Output operation clock for the CPU.                                                                                                                                                                                                                                                                                                                                                       |

|      |                                      | HOLD                               | I   | While the HOLD pin input is "L", the MCU is placed in the Hold state.                                                                                                                                                                                                                                                                                                                     |

|      |                                      | HLDA                               | 0   | The HLDA pin output is "L" while the MCU is in the hold state.                                                                                                                                                                                                                                                                                                                            |

|      |                                      | ALE                                | 0   | The ALE pin can be used to latch the address.                                                                                                                                                                                                                                                                                                                                             |

|      |                                      | RDY                                | - 1 | While the RDY pin input is "L", the MCU is in the ready state.                                                                                                                                                                                                                                                                                                                            |

# Table 1.3 Pin description

| Port | Function                 | Pin Name                                                               | I/O  | Description                                                                                                                                                                                |

|------|--------------------------|------------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6   | I/O port                 | P6 <sub>0</sub> to P6 <sub>7</sub>                                     | I/O  | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                |

|      | UART/SSI                 | CTS/RTS/SS/WS<br>CLK/SCK<br>RxD/SCL/STxD/RX<br>TxD/SDA/SRxD/XMT        | I/O  | $P6_0$ to $P6_3$ are I/O ports for UART0.<br>$P6_4$ to $P6_7$ are I/O ports for UART1.<br>These pins can be used for Serial Sound Interface, I <sup>2</sup> C and SPI communication.       |

| P7   | I/O port                 | P7 <sub>0</sub> to P7 <sub>7</sub>                                     | I/O  | This is an 8-bit I/O port equivalent to P0. $P7_0$ and $P7_1$ are N-channel open drain output.                                                                                             |

|      | Timer A                  | TAIN                                                                   | I    | P7 <sub>0</sub> to P7 <sub>7</sub> are I/O ports for Timer A0 to A3.                                                                                                                       |

|      |                          | TAout                                                                  | 0    |                                                                                                                                                                                            |

|      | UART                     | CTS/RTS/SS/WS<br>CLK/SCK<br>RxD/SCL/STxD<br>TxD/SDA/SRxD               | I/O  | P7 <sub>0</sub> to P7 <sub>3</sub> are I/O ports for UART2. P7 <sub>4</sub> to P7 <sub>7</sub> are I/O ports for UART3. These pins can be used for I <sup>2</sup> C and SPI communication. |

|      | LED drive                | LED <sub>0</sub> to LED <sub>7</sub>                                   | 0    | These pins are capable of sinking 20mA for driving LEDs.                                                                                                                                   |

| P8   | I/O port                 | P8 <sub>0</sub> to P8 <sub>4</sub> , P8 <sub>6</sub> , P8 <sub>7</sub> | I/O  | This is a 7-bit I/O port equivalent to P0.                                                                                                                                                 |

|      | External interrupt input | INT0 to INT2                                                           | I    | P82 to P84 are external interrupt input ports.                                                                                                                                             |

|      | Input                    | P8 <sub>5</sub> /NMI                                                   | I    | Input port for NMI interrupt.                                                                                                                                                              |

|      | Sub-Clock                | XCIN, XCOUT                                                            | I, O | P8 <sub>6</sub> and P8 <sub>7</sub> , connect an oscillator between these pins for sub-clock generation.                                                                                   |

| P9   | I/O port                 | P9 <sub>0</sub> , P9 <sub>2</sub> , P9 <sub>3</sub>                    | I/O  | This is a 3-bit I/O port equivalent to P0.                                                                                                                                                 |

|      | A/D                      | AD <sub>TRG</sub>                                                      | I    | P9 <sub>3</sub> is an A/D trigger input port.                                                                                                                                              |

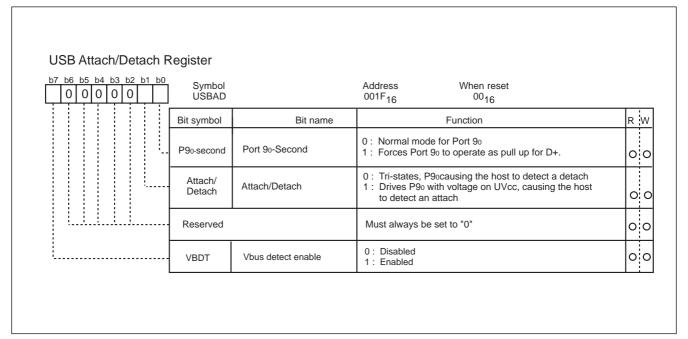

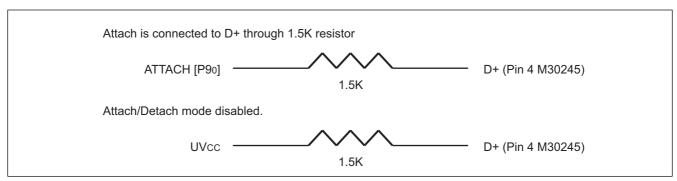

|      | USB-ATTACH               | ATTACH                                                                 | 0    | ${\rm P9_0}$ can be used to attach or detach from the USB host without disconnecting the USB cable.                                                                                        |

|      | USB SOF                  | SOF                                                                    | 0    | P92 is an output for the USB start of frame signal pulse.                                                                                                                                  |

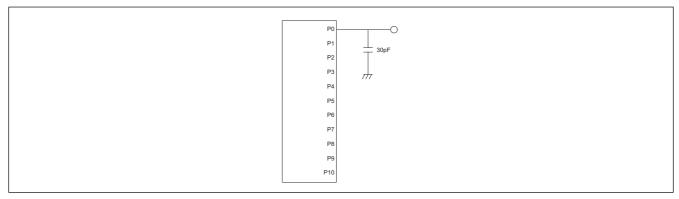

| P10  | I/O port                 | P10 <sub>0</sub> to P10 <sub>7</sub>                                   | I/O  | This is an 8-bit I/O port equivalent to P0.                                                                                                                                                |

|      | Key-input interrupt      | KI <sub>0</sub> to KI <sub>7</sub>                                     | I    | P10 <sub>0</sub> to P10 <sub>7</sub> are key-input interrupt ports.                                                                                                                        |

|      | Analog input             | AN <sub>0</sub> to AN <sub>7</sub>                                     | I    | P10 <sub>0</sub> to P10 <sub>7</sub> are analog input ports for A/D converter.                                                                                                             |

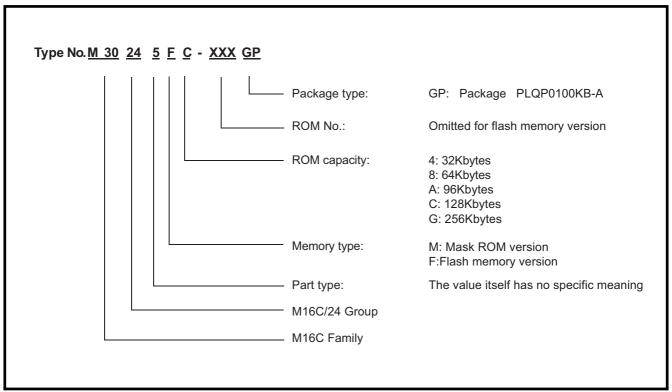

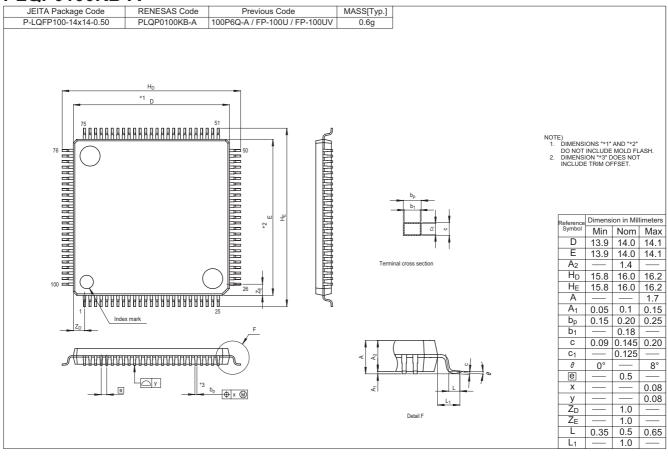

Renesas plans to release the following products in the M30245 group:

- (1) Support for Flash memory version and mask ROM versions

- (2) ROM capacity: 128 or 64 Kbytes

- (3) Package: 100P6Q-A Plastic molded LQFP

Figure 1.3 shows the type number, memory size and package for the M30245 group. Table 1.4 lists the package number, type, ROM and RAM capacity for the M30245 group.

Figure 1.3. Type number, memory size, and package

Table 1.4. Package number, type, ROM and RAM capacity for M30245 group

| Туре           | ROM Capacity | RAM Capacity | Package Type | Remarks              |

|----------------|--------------|--------------|--------------|----------------------|

| M30245FCGP     | 128K bytes   | 10K bytes    | PLQP0100KB-A | Flash Memory Version |

| M30245MC-XXXGP | 128K bytes   | 10K bytes    | PLQP0100KB-A | Mask ROM Version     |

| M30245M8-XXXGP | 64K bytes    | 5K bytes     | PLQP0100KB-A | Mask ROM Version     |

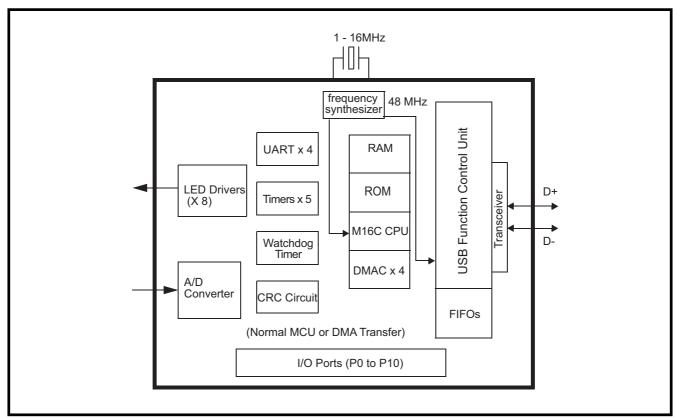

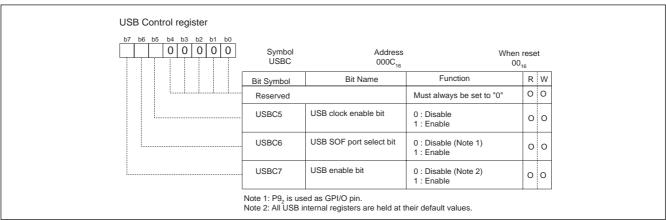

#### **USB Overview**

The M30245 group is a single-chip PC peripheral microcontroller that is compliant with the Universal Serial Bus (USB) Version 2.0 specification for full-speed USB operation (12Mbps). This device provides an interface between a USB-equipped host computer and PC peripherals such as telephones, audio systems, and digital cameras. The M30245 architectural overview is shown in Figure 1.4.

The USB function control unit of the M30245 group supports full-speed operation and all four data transfer types listed in the USB specification. Each transfer type is used for controlling a different set of PC peripherals.

- **Isochronous transfers** provide guaranteed bus access, a constant data rate, and error tolerance for devices such as computer-telephone integration (CTI) and audio systems.

- Interrupt transfers are designed to support human input devices (HID) that communicate small amounts of data infrequently.

- Bulk transfers are necessary for devices such as digital cameras and scanners that communicate large amounts of data to the PC as bus bandwidth becomes free.

- **Control transfers** are supported and are useful for bursty, host-initiated type communication where bus management is the primary concern.

Figure 1.4. M30245 architectural overview

# **Functional Block Operation**

The M30245 group contains many functional blocks in a single chip. These blocks include ROM and RAM to store instructions and data and the central processing unit (CPU) to execute arithmetic/logic operations. Also included are peripheral blocks such as Timer A, serial I/O, DMAC, CRC calculation circuit, A/D converter, and I/O ports.

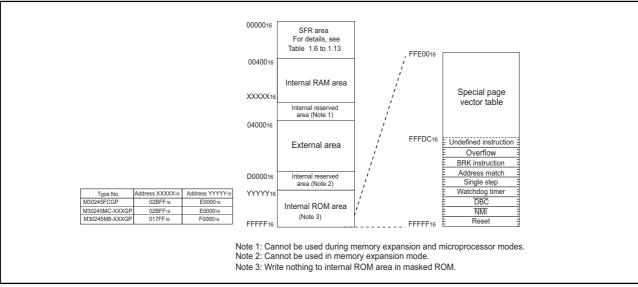

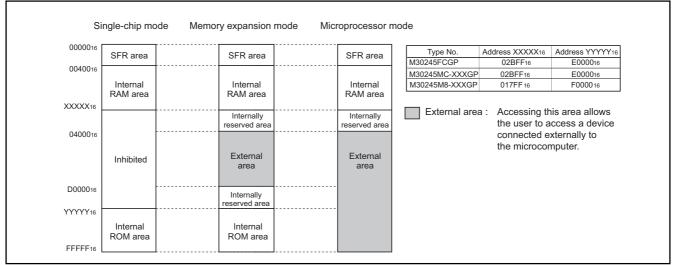

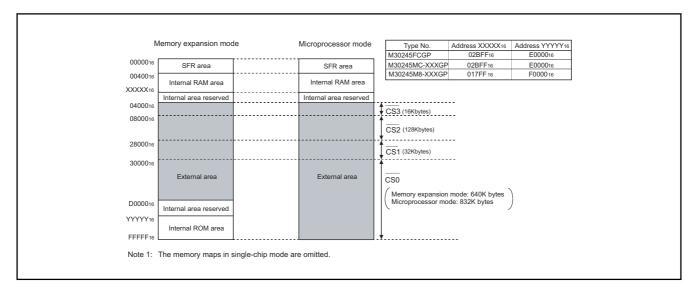

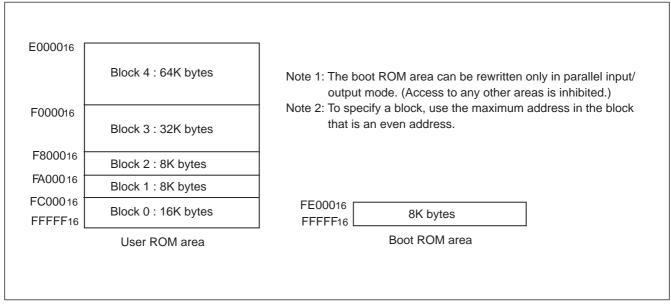

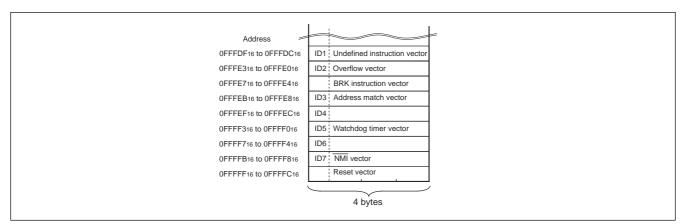

## Memory

Figure 1.5 is a memory map of the M30245 group. The address space extends the 1M bytes from address 0000016 to FFFFF16. From FFFFF16 down is ROM. For example, in the M30245MC-XXXGP, there is 128K bytes of internal ROM from E000016 to FFFFF16. The vector table for fixed interrupts such as the reset and  $\overline{\text{NMI}}$  are mapped to FFFDC16 to FFFF16. The starting address of the interrupt routine is stored here. The address of the vector table for timer interrupts, etc., can be set as desired using the internal register (INTB). See the section on interrupts for details.

From 0040016 up is RAM. For example, in the M30245MC-XXXGP, 10K bytes of internal RAM is mapped to the space from 0040016 to 02BFF16. In addition to storing data, the RAM also stores the stack used when calling subroutines and when interrupts are generated.

The SFR area is mapped to 0000016 to 003FF16. This area accommodates the control registers for peripheral devices such as I/O ports, A/D converter, serial I/O, and timers, etc. Any part of the SFR area that is not occupied is reserved and cannot be used for other purposes.

The special page vector table is mapped to FFE0016 to FFFDB16. If the starting addresses of subroutines or the destination addresses of jumps are stored here, subroutine call instructions and jump instructions can be used as 2-byte instructions, reducing the number of program steps.

In memory expansion mode and microprocessor mode, some memory areas are reserved and cannot be used. For example, in the M30245MC-XXXGP, the following areas cannot be used.

- The space between 02C0016 and 03FFF16 (Memory expansion and microprocessor modes)

- The space between D000016 and E000016 (Memory expansion mode)

Figure 1.5. Memory map

M30245 Group Central Processing Unit

## **Central Processing Unit**

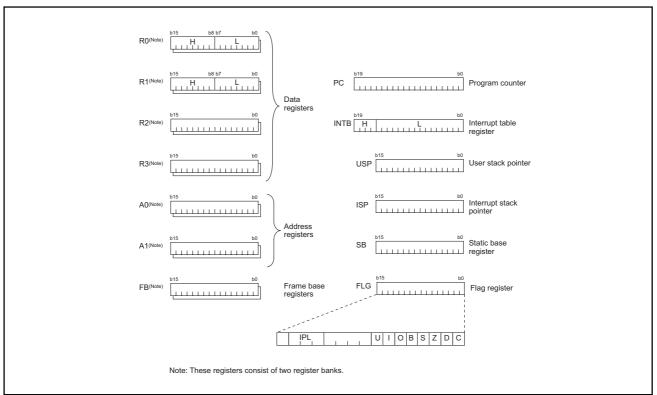

The CPU has a total of 13 registers shown in Figure 1.6. Seven of these registers (R0, R1, R2, R3, A0, A1, and FB) come in two sets; therefore, these have two register banks.

Figure 1.6. Central processing unit register

# Data registers (R0, R0H, R0L, R1, R1H, R1L, R2, and R3)

Data registers (R0, R1, R2, and R3) are configured with 16 bits, and are used primarily for transfer and arithmetic/logic operations.

Registers R0 and R1 each can be used as separate 8-bit data registers, high-order bits as (R0H/R1H), and low-order bits as (R0L/R1L). In some instructions, registers R2 and R0, as well as R3 and R1 can use as 32-bit data registers (R2R0/R3R1).

# Address registers (A0 and A1)

Address registers (A0 and A1) are configured with 16 bits, and have functions equivalent to those of data registers. These registers can also be used for address register indirect addressing and address register relative addressing.

In some instructions, registers A1 and A0 can be combined for use as a 32-bit address register (A1A0).

## Frame base register (FB)

Frame base register (FB) is configured with 16 bits, and is used for FB relative addressing.

M30245 Group Central Processing Unit

#### Program counter (PC)

Program counter (PC) is configured with 20 bits, indicating the address of an instruction to be executed.

### Interrupt table register (INTB)

Interrupt table register (INTB) is configured with 20 bits, indicating the start address of an interrupt vector table.

#### Stack pointer (USP/ISP)

The stack pointer comes in two types: user stack pointer (USP) and interrupt stack pointer (ISP), each configured with 16 bits.

The desired type of stack pointer (USP or ISP) can be selected by the stack pointer select flag (U flag). This flag is located at bit 7 of the flag register (FLG).

#### Static base register (SB)

Static base register (SB) is configured with 16 bits, and is used for SB relative addressing.

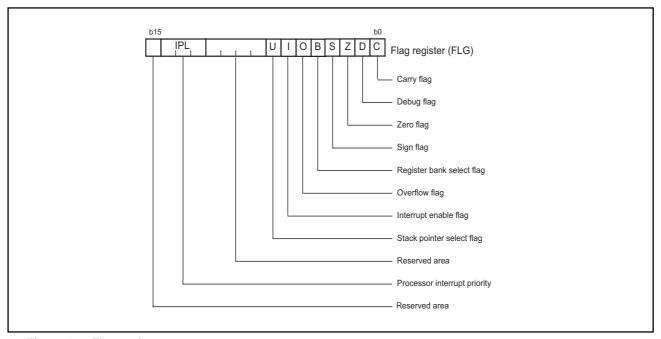

#### Flag register (FLG)

Flag register (FLG) is configured with 11 bits, each bit is used as a flag. Figure 1.7 shows the flag register (FLG). The following explains the function of each flag:

#### • Bit 0: Carry flag (C flag)

This flag retains a carry, borrow, or shift-out bit that has occurred in the arithmetic/logic unit.

#### • Bit 1: Debug flag (D flag)

This flag enables a single-step interrupt.

When this flag is "1", a single-step interrupt is generated after instruction execution. This flag is cleared to "0" when the interrupt is acknowledged.

## • Bit 2: Zero flag (Z flag)

This flag is set to "1" when an arithmetic operation resulted in 0; otherwise, cleared to "0".

#### • Bit 3: Sign flag (S flag)

This flag is set to "1" when an arithmetic operation resulted in a negative value; otherwise, cleared to "0".

#### • Bit 4: Register bank select flag (B flag)

This flag chooses a register bank. Register bank 0 is selected when this flag is "0"; register bank 1 is selected when this flag is "1".

# • Bit 5: Overflow flag (O flag)

This flag is set to "1" when an arithmetic operation resulted in overflow; otherwise, cleared to "0".

#### • Bit 6: Interrupt enable flag (I flag)

This flag enables all maskable interrupts.

Interrupts are disabled when this flag is "0", and are enabled when this flag is "1". This flag is cleared to "0" when an interrupt is acknowledged.

M30245 Group Central Processing Unit

#### • Bit 7: Stack pointer select flag (U flag)

Interrupt stack pointer (ISP) is selected when this flag is "0"; user stack pointer (USP) is selected when this flag is "1".

This flag is cleared to "0" when a hardware interrupt is acknowledged or an INT instruction of software interrupt Nos. 0 to 31 is executed.

#### • Bits 8 to 11: Reserved area

## • Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is enabled.

#### • Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the software manual for details.

Figure 1.7. Flag register

M30245 Group Reset

#### Reset

There are two kinds of resets: software and hardware. In both cases, operation is the same after the reset.

#### **Software Reset**

Writing a "1" to bit 3 of the processor mode register 0 (address 000416) applies a (software) reset to the microcomputer. A software reset has almost the same effect as a hardware reset with the following exceptions:

- The contents of internal RAM are preserved in a software reset.

- The contents of all USB and PLL SFR values are preserved in a software reset.

- For bit 0 and 1 of processor mode register 0 (address 000416), and bit 1 of pull-up control register 1 (address 03FD16), the value after software reset will be different from the value after hardware reset.

When performing a software reset, select the main clock for the CPU clock source, and set the PM03 bit to "1" only when the main clock is stabilized.

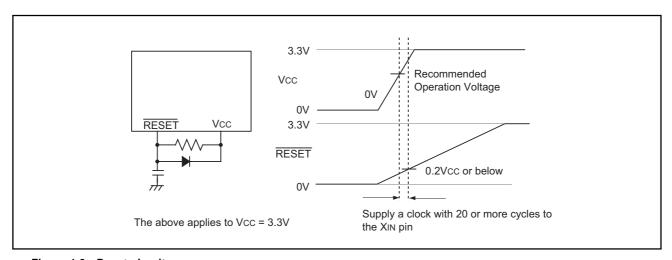

#### Hardware reset

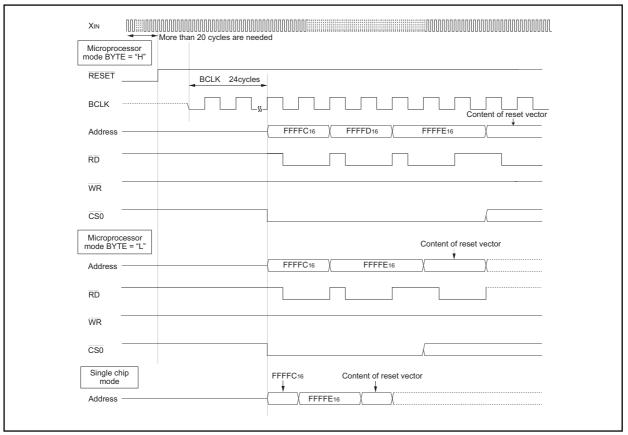

When the supply voltage is in the range where operation is guaranteed, a reset is executed by holding the reset pin to "L" level (0.2VCC max.) for at least 20 cycles. When the reset pin level is then returned to the "H" level while the main clock is stable, the device exits reset and the program execution resumes from the address in the reset vector table.

Figure 1.8 shows an example reset circuit. Figure 1.9 shows the reset sequence.

Figure 1.8. Reset circuit

#### I/O Status during Reset

When the RESET pin level is "L", all ports change to input mode (floating) Table 1.5 shows the status of the other pins while the RESET pin level is "L".

M30245 Group Reset

Figure 1.9. Reset sequence

Table 1.5. Pin status when RESET pin level is "L"

|                                                                                             | Status                |                                                                     |                                                                     |  |  |  |  |

|---------------------------------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| Pin name                                                                                    | CNVss=Vss             | CNVss=                                                              | Vcc                                                                 |  |  |  |  |

|                                                                                             | CNVSS=VSS             | BYTE=Vss                                                            | BYTE=Vcc                                                            |  |  |  |  |

| P <sub>0</sub>                                                                              | Input port (floating) | Data input (floating)                                               | Data input (floating)                                               |  |  |  |  |

| P <sub>1</sub>                                                                              | Input port (floating) | Data input (floating)                                               | Input port (floating)                                               |  |  |  |  |

| P <sub>2</sub> ,P <sub>3</sub> , P4 <sub>0</sub> to P4 <sub>3</sub>                         | Input port (floating) | Address output (undefined)                                          | Address output (undefined)                                          |  |  |  |  |

| P4 <sub>4</sub>                                                                             | Input port (floating) | CS0 output ("H" level is output)                                    | CS0 output ("H" level is output)                                    |  |  |  |  |

| P4 <sub>5</sub> to P4 <sub>7</sub>                                                          | Input port (floating) | Input port (floating)<br>(pull-up resistor is on)                   | Input port (floating)<br>(pull-up resistor is on)                   |  |  |  |  |

| P5 <sub>0</sub>                                                                             | Input port (floating) | WR output ("H" level is output)                                     | WR output ("H" level is output)                                     |  |  |  |  |

| P5 <sub>1</sub>                                                                             | Input port (floating) | BHE output (undefined)                                              | BHE output (undefined)                                              |  |  |  |  |

| P5 <sub>2</sub>                                                                             | Input port (floating) | RD output ("H" level is output)                                     | RD output ("H" level is output)                                     |  |  |  |  |

| P5 <sub>3</sub>                                                                             | Input port (floating) | BCLK output                                                         | BCLK output                                                         |  |  |  |  |

| P5 <sub>4</sub>                                                                             | Input port (floating) | HLDA output (The output value depends on the input to the HOLD pin) | HLDA output (The output value depends on the input to the HOLD pin) |  |  |  |  |

| P5 <sub>5</sub>                                                                             | Input port (floating) | HOLD input (floating)                                               | HOLD input (floating)                                               |  |  |  |  |

| P5 <sub>6</sub>                                                                             | Input port (floating) | ALE output ("L" level is output)                                    | ALE output ("L" level is output)                                    |  |  |  |  |

| P5 <sub>7</sub>                                                                             | Input port (floating) | RDY input (floating)                                                | RDY input (floating)                                                |  |  |  |  |

| P6, P7, P8 <sub>0</sub> to P8 <sub>4</sub> ,<br>P8 <sub>6</sub> , P8 <sub>7</sub> , P9, P10 | Input port (floating) | Input port (floating)                                               | Input port (floating)                                               |  |  |  |  |

# **Special Function Registers**

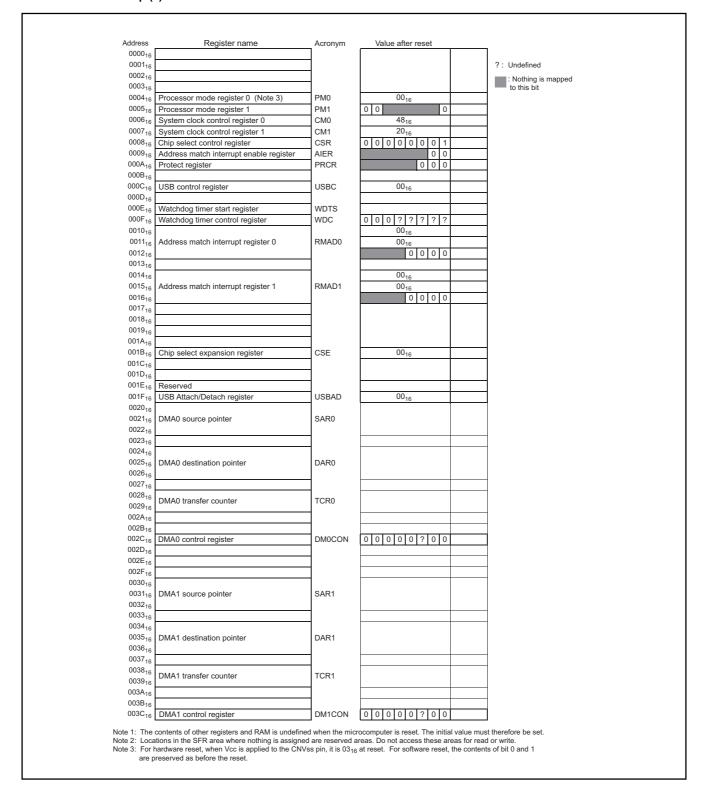

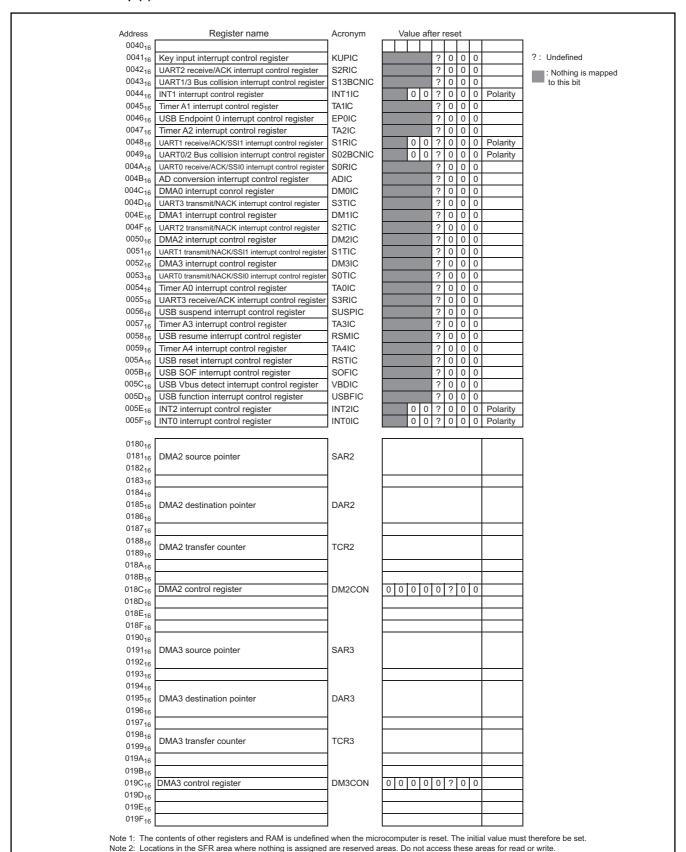

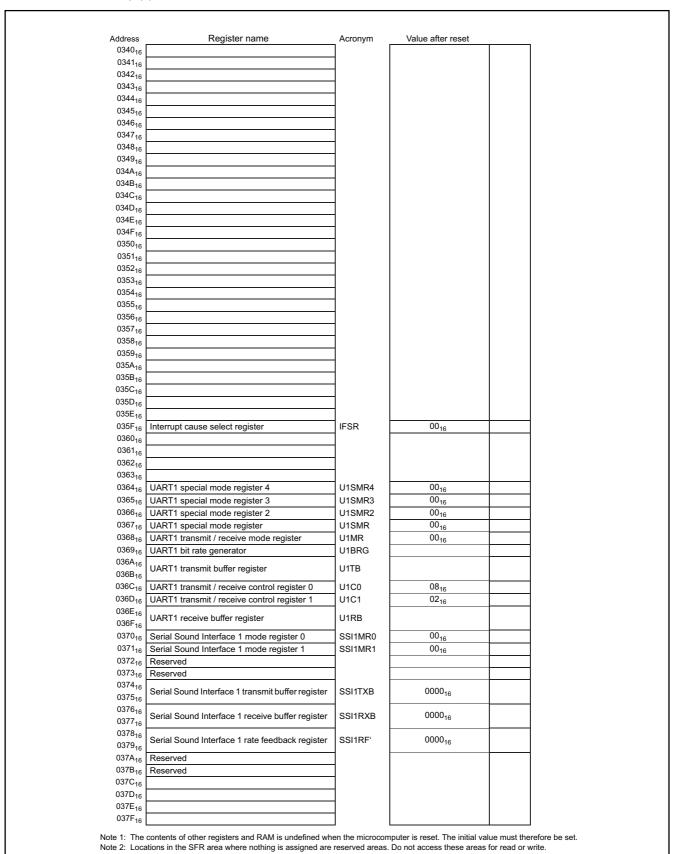

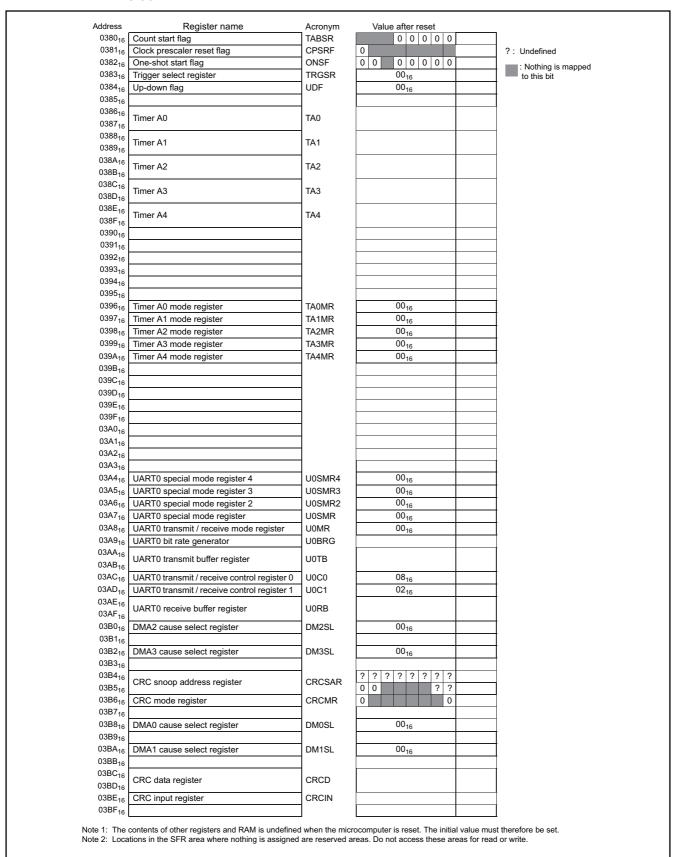

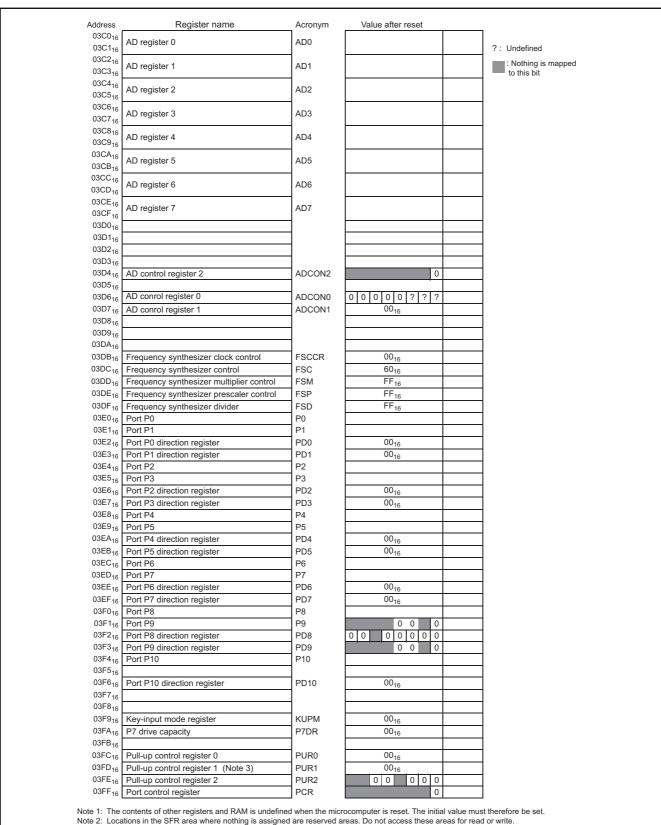

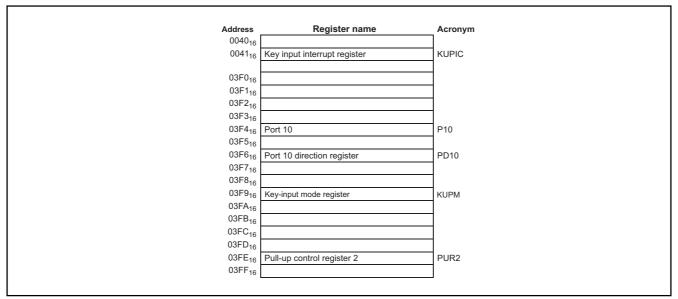

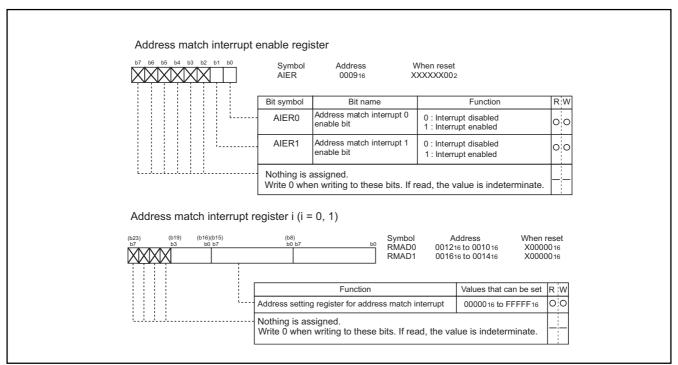

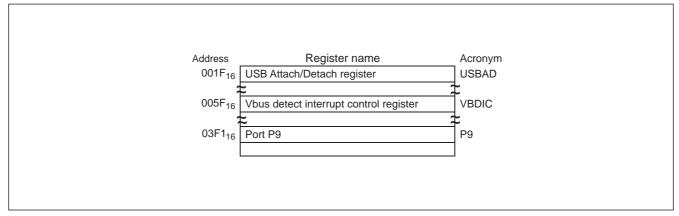

Tables 1.6 to 1.13 show the peripheral control registers, their addresses, names, acronyms, and values after reset.

Table 1.6. SFR Map (1)

Table 1.7. SFR Map (2)

Table 1.8. SFR Map (3)

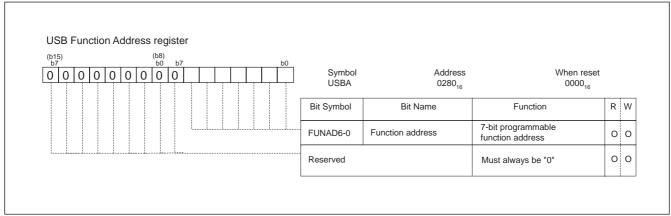

| Address                                  | Register name                           | Acronym | Value after reset  |

|------------------------------------------|-----------------------------------------|---------|--------------------|

| 0280 <sub>16</sub>                       | USB address register                    | USBA    | 0000 <sub>16</sub> |

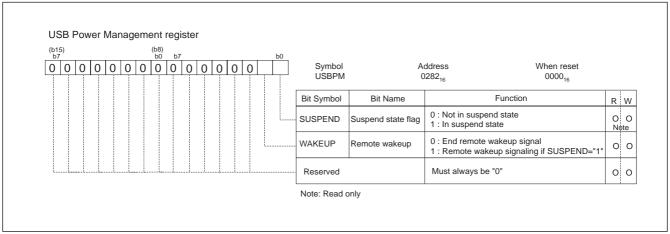

| 0281 <sub>16</sub><br>0282 <sub>16</sub> | USB power management register           | USBPM   | 000016             |

| 0283 <sub>16</sub><br>0284 <sub>16</sub> | OSB power management register           | OSBFIN  | 000016             |

| 0285 <sub>16</sub>                       | USB interrupt status register           | USBIS   | 0000 <sub>16</sub> |

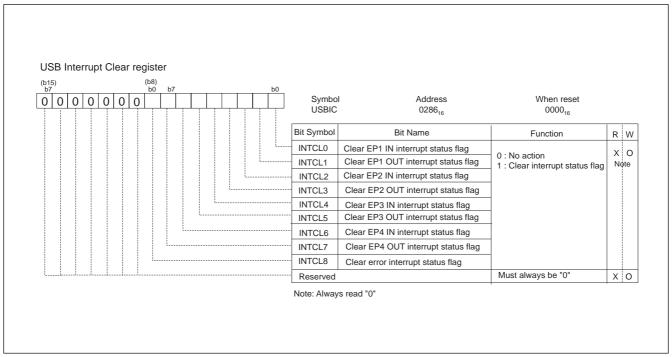

| 0286 <sub>16</sub><br>0287 <sub>16</sub> | USB interrupt clear register            | USBIC   | 0000 <sub>16</sub> |

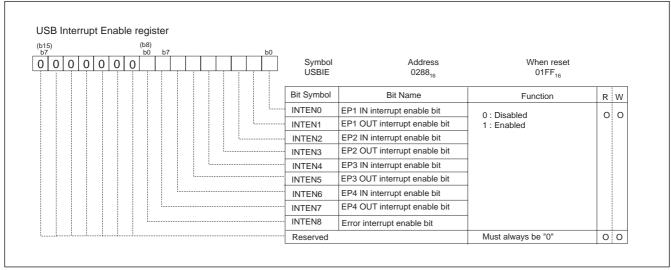

| 0288 <sub>16</sub><br>0289 <sub>16</sub> | USB interrupt enable register           | USBIE   | 01FF <sub>16</sub> |

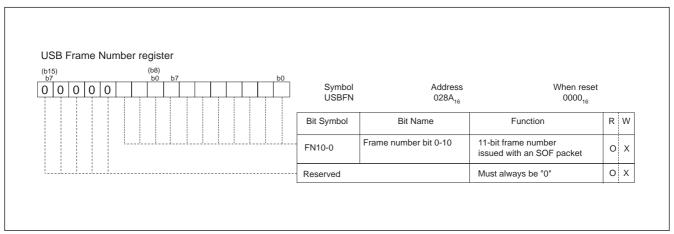

| 028A <sub>16</sub><br>028B <sub>16</sub> | USB frame number register               | USBFN   | 0000 <sub>16</sub> |

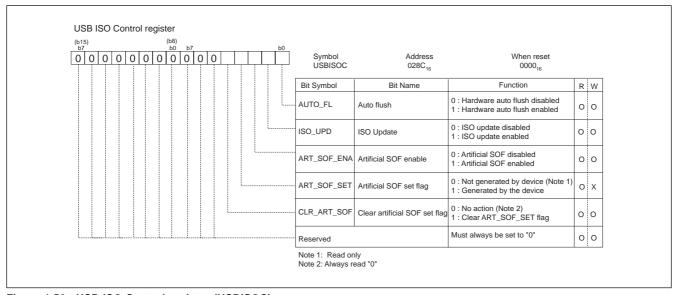

| 028C <sub>16</sub><br>028D <sub>16</sub> | USB ISO control register                | USBISOC | 0000 <sub>16</sub> |

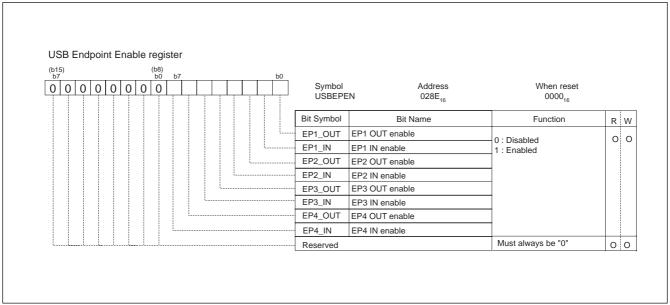

| 028E <sub>16</sub><br>028F <sub>16</sub> | USB endpoint enable register            | USBEPEN | 0000 <sub>16</sub> |

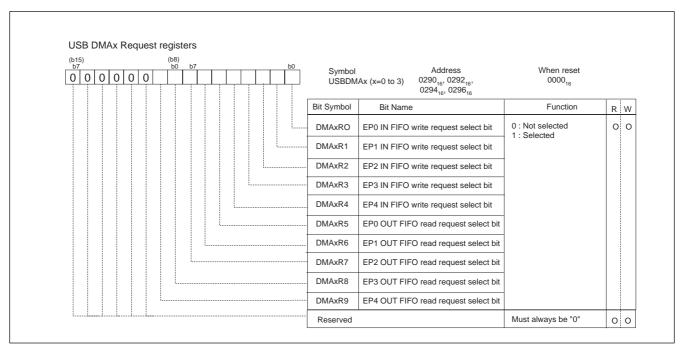

| 0290 <sub>16</sub><br>0291 <sub>16</sub> | USB DMA0 request register               | USBDMA0 | 0000 <sub>16</sub> |

| 0292 <sub>16</sub><br>0293 <sub>16</sub> | USB DMA1 request register               | USBDMA1 | 0000 <sub>16</sub> |

| 0294 <sub>16</sub><br>0295 <sub>16</sub> | USB DMA2 request register               | USBDMA2 | 0000 <sub>16</sub> |

| 0296 <sub>16</sub><br>0297 <sub>16</sub> | USB DMA3 request register               | USBDMA3 | 0000 <sub>16</sub> |

| 0298 <sub>16</sub><br>0299 <sub>16</sub> | USB EP0 control/status register         | EP0CS   | 2000 <sub>16</sub> |

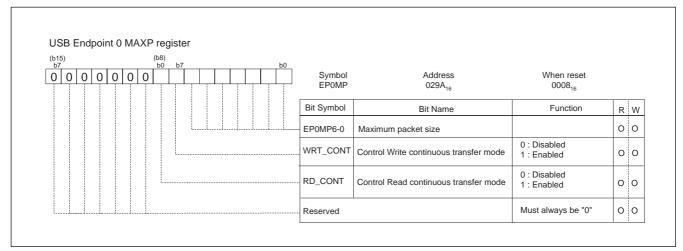

| 029A <sub>16</sub><br>029B <sub>16</sub> | USB EP0 max packet size register        | EP0MP   | 0008 <sub>16</sub> |

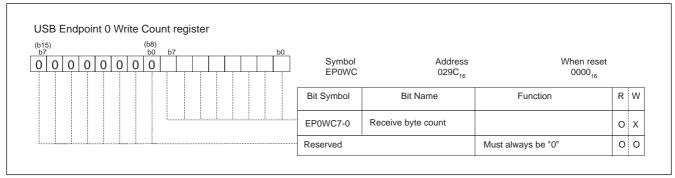

| 029C <sub>16</sub><br>029D <sub>16</sub> | USB EP0 write count register            | EP0WC   | 0000 <sub>16</sub> |

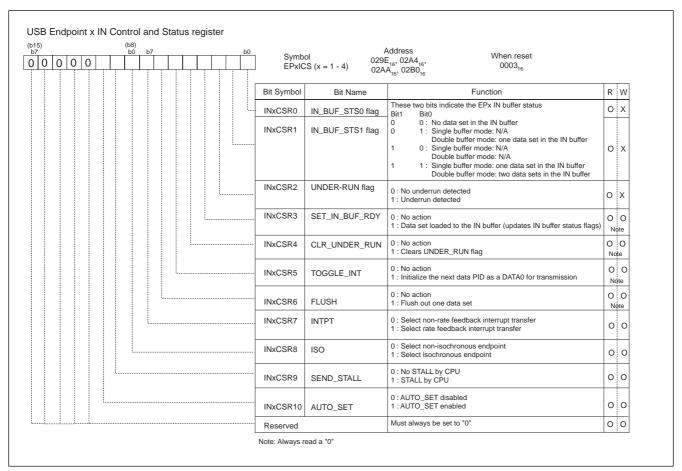

| 029E <sub>16</sub><br>029F <sub>16</sub> | USB EP1 IN control/status register      | EP1ICS  | 0003 <sub>16</sub> |

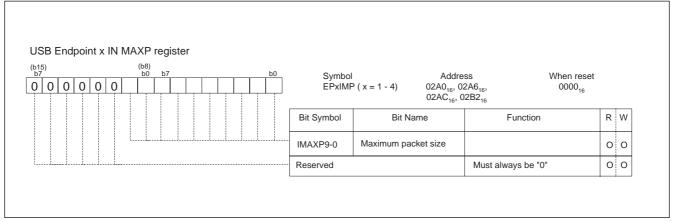

| 02A0 <sub>16</sub><br>02A1 <sub>16</sub> | USB EP1 IN max packet size register     | EP1IMP  | 0000 <sub>16</sub> |

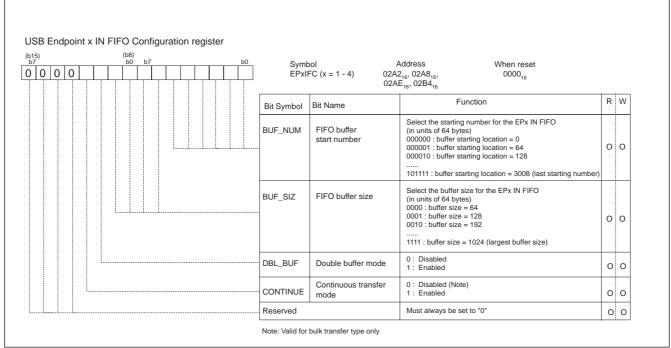

| 02A2 <sub>16</sub><br>02A3 <sub>16</sub> | USB EP1 IN FIFO configuration register  | EP1IFC  | 0000 <sub>16</sub> |

| 02A4 <sub>16</sub><br>02A5 <sub>16</sub> | USB EP2 IN control/status register      | EP2ICS  | 0003 <sub>16</sub> |

| 02A6 <sub>16</sub><br>02A7 <sub>16</sub> | USB EP2 IN max packet size register     | EP2IMP  | 0000 <sub>16</sub> |

| 02A8 <sub>16</sub><br>02A9 <sub>16</sub> | USB EP2 IN FIFO configuration register  | EP2IFC  | 0000 <sub>16</sub> |

| 02AA <sub>16</sub><br>02AB <sub>16</sub> | USB EP3 IN control/status register      | EP3ICS  | 0003 <sub>16</sub> |

| 02AC <sub>16</sub><br>02AD <sub>16</sub> | USB EP3 IN max packet size register     | EP3IMP  | 0000 <sub>16</sub> |

| 02AE <sub>16</sub><br>02AF <sub>16</sub> | USB EP3 IN FIFO configuration register  | EP3IFC  | 0000 <sub>16</sub> |

| 02B0 <sub>16</sub><br>02B1 <sub>16</sub> | USB EP4 IN control/status register      | EP4ICS  | 0003 <sub>16</sub> |

| 02B2 <sub>16</sub><br>02B3 <sub>16</sub> | USB EP4 IN max packet size register     | EP4IMP  | 0000 <sub>16</sub> |

| 02B4 <sub>16</sub><br>02B5 <sub>16</sub> | USB EP4 IN FIFO configuration register  | EP4IFC  | 0000 <sub>16</sub> |

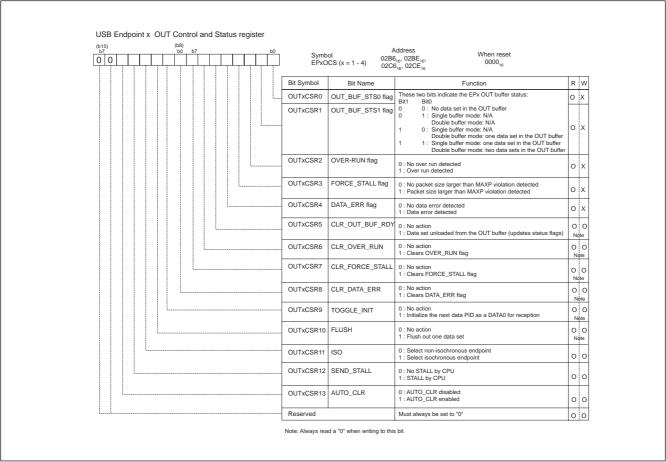

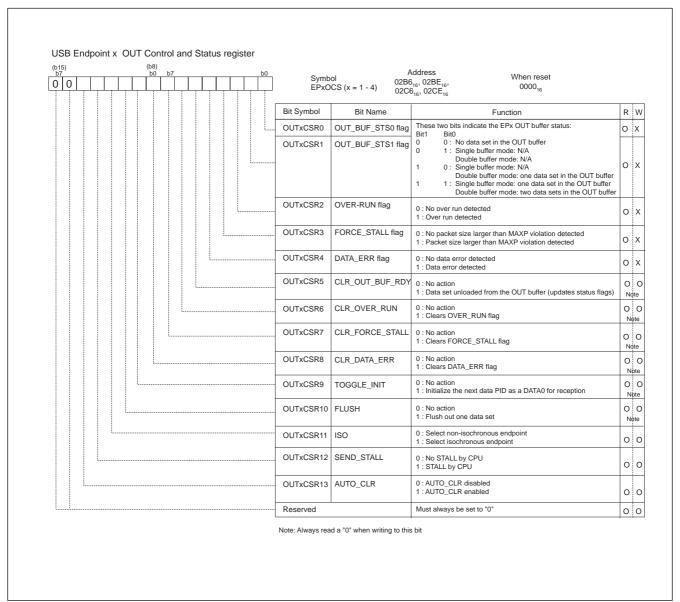

| 02B6 <sub>16</sub><br>02B7 <sub>16</sub> | USB EP1 OUT control/status register     | EP10CS  | 0000 <sub>16</sub> |

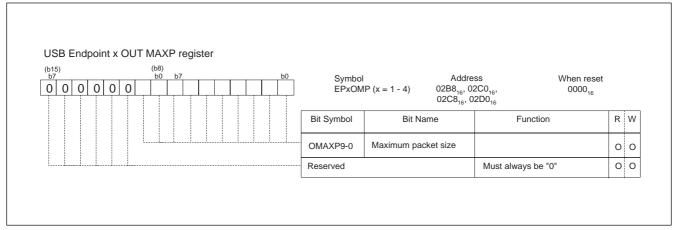

| 02B8 <sub>16</sub><br>02B9 <sub>16</sub> | USB EP1 OUT max packet size register    | EP10MP  | 0000 <sub>16</sub> |

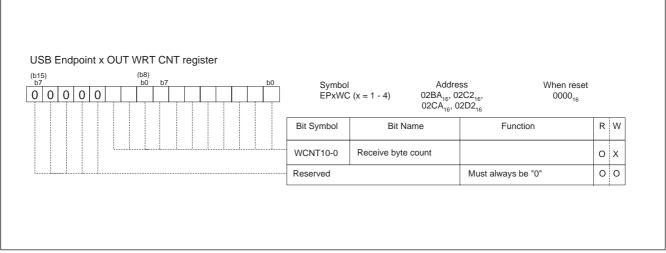

| 02BA <sub>16</sub><br>02BB <sub>16</sub> | USB EP1 OUT write count register        | EP1WC   | 0000 <sub>16</sub> |

| 02BC <sub>16</sub><br>02BD <sub>16</sub> | USB EP1 OUT FIFO configuration register | EP10FC  | 0000 <sub>16</sub> |

| 02BE <sub>16</sub><br>02BF <sub>16</sub> | USB EP2 OUT control /status register    | EP2OCS  | 0000 <sub>16</sub> |

Note 1: The contents of other registers and RAM is undefined when the microcomputer is reset. The initial value must therefore be set. Note 2: Locations in the SFR area where nothing is assigned are reserved areas. Do not access these areas for read or write.

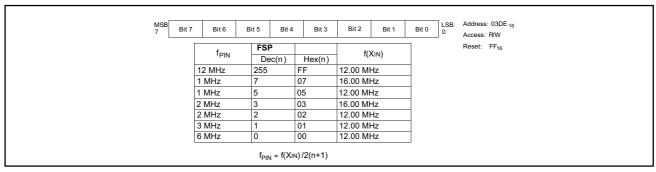

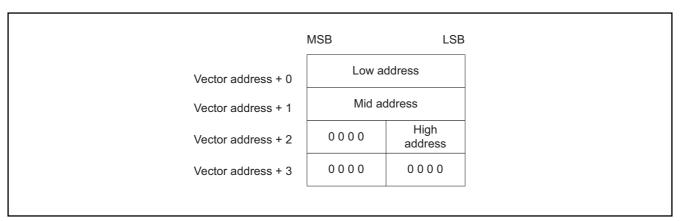

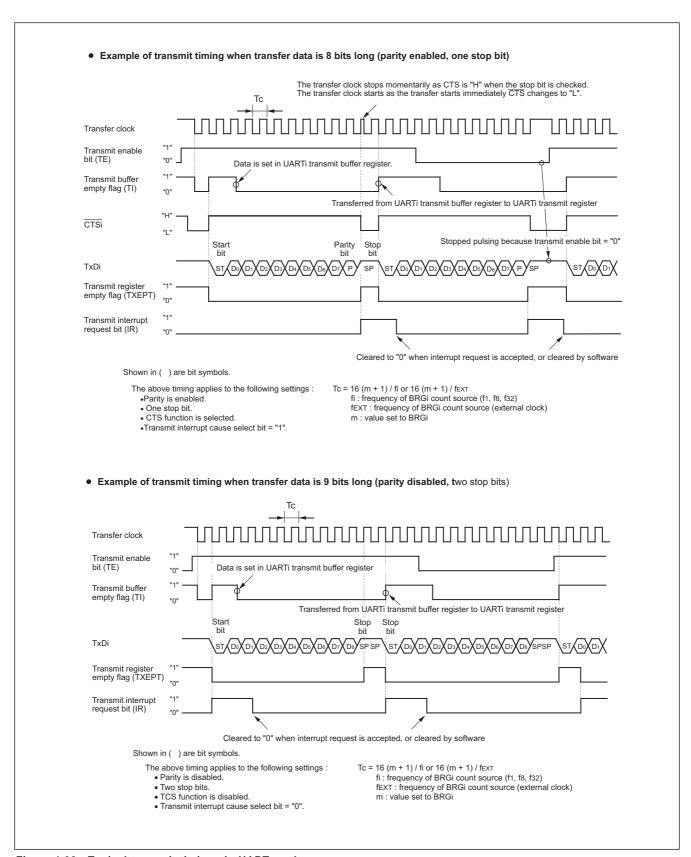

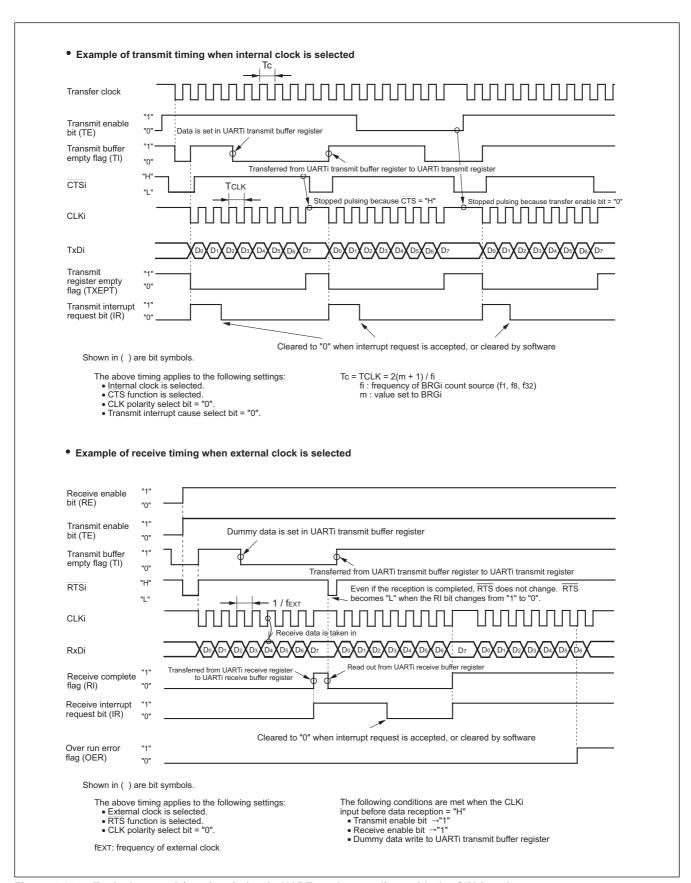

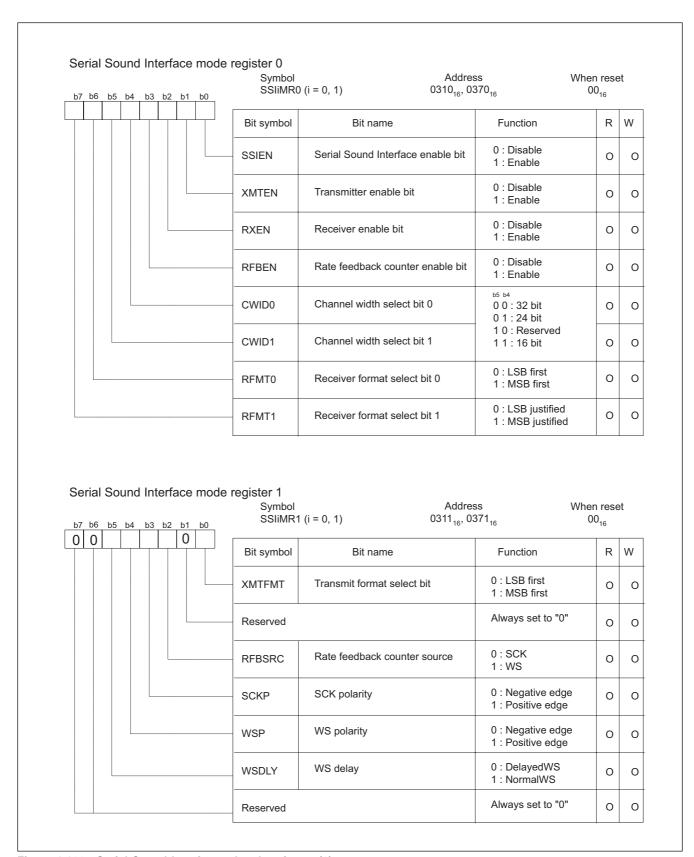

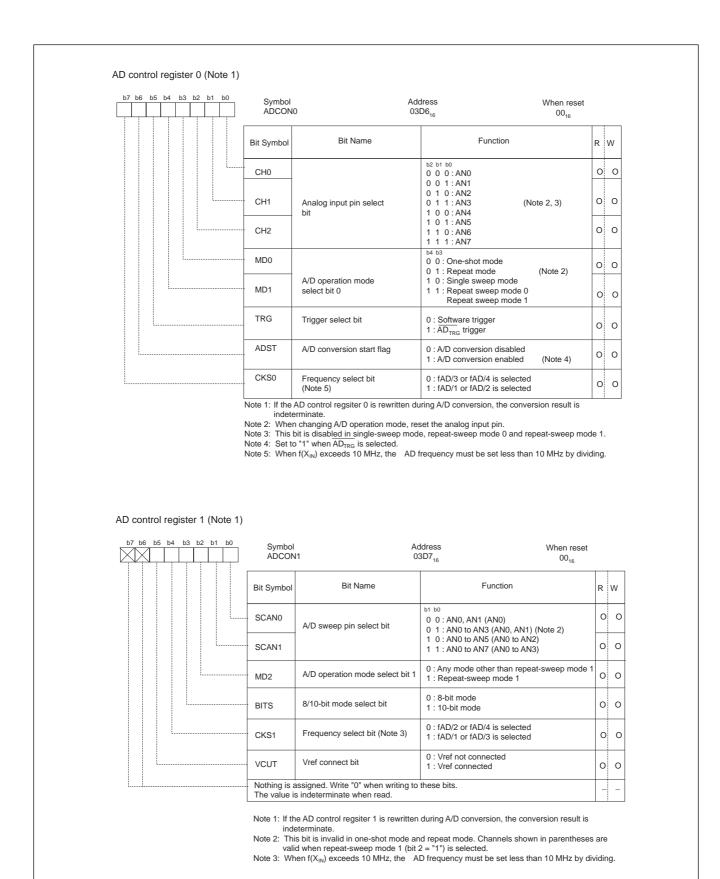

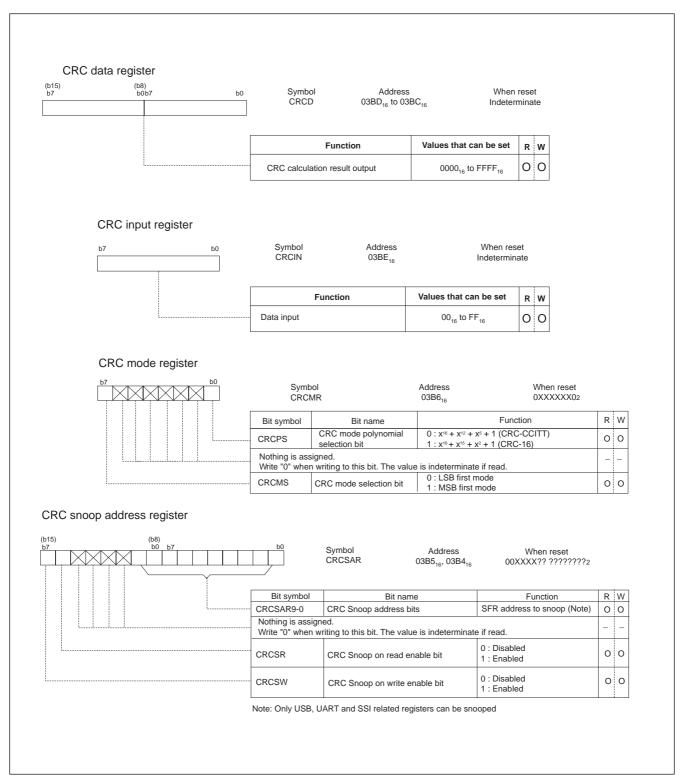

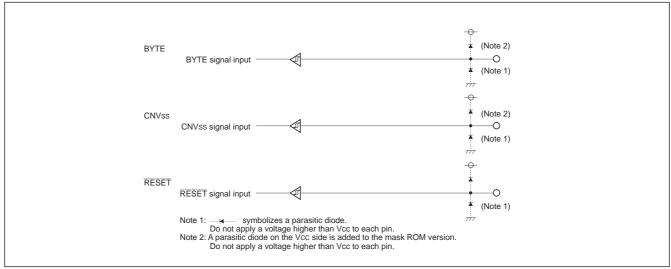

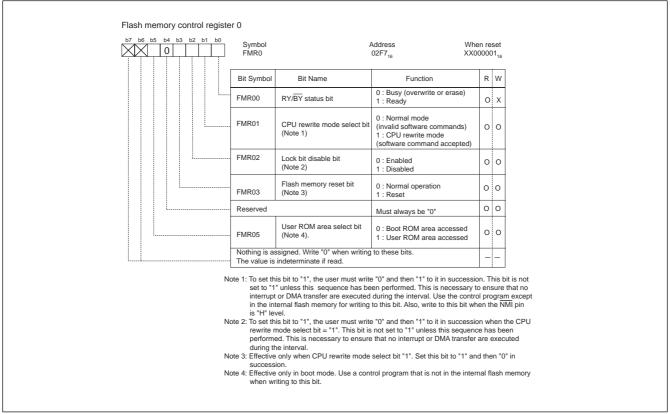

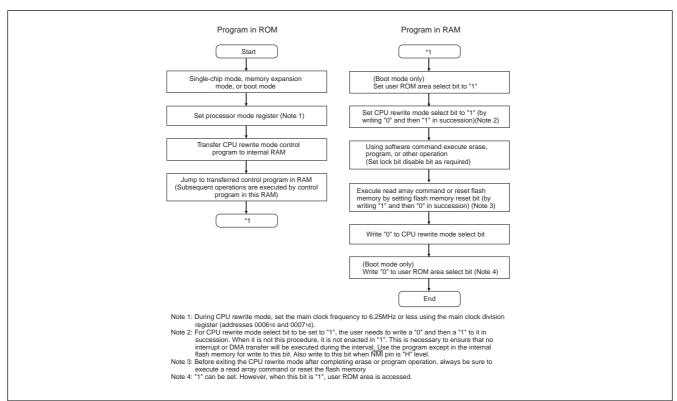

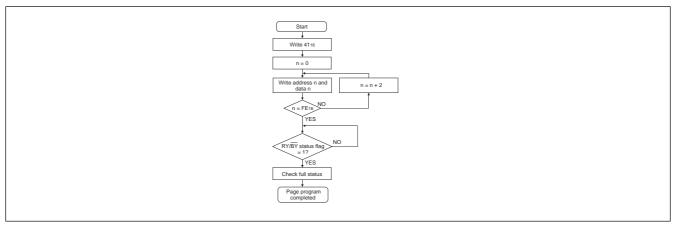

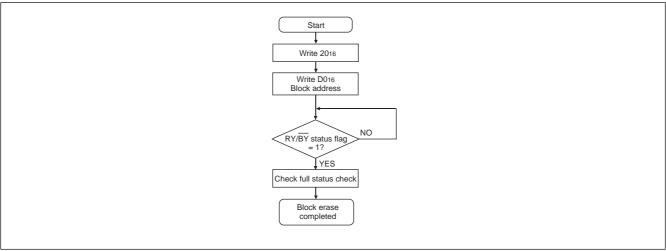

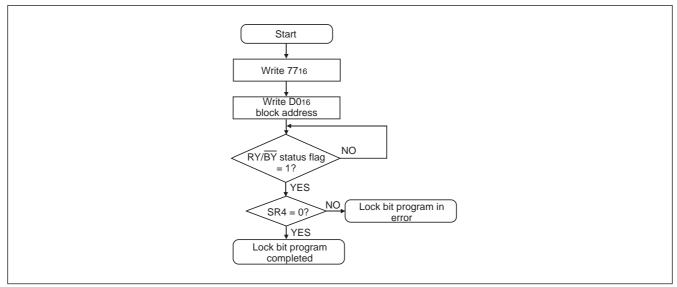

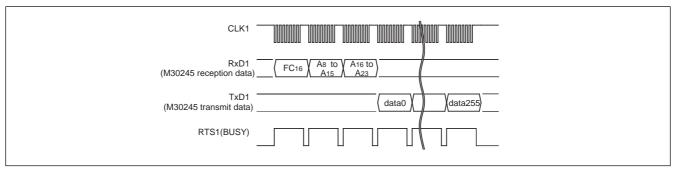

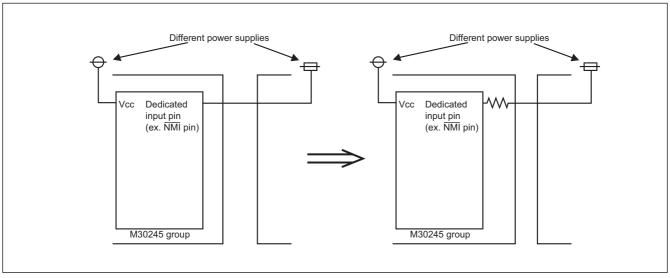

Table 1.9. SFR Map (4)